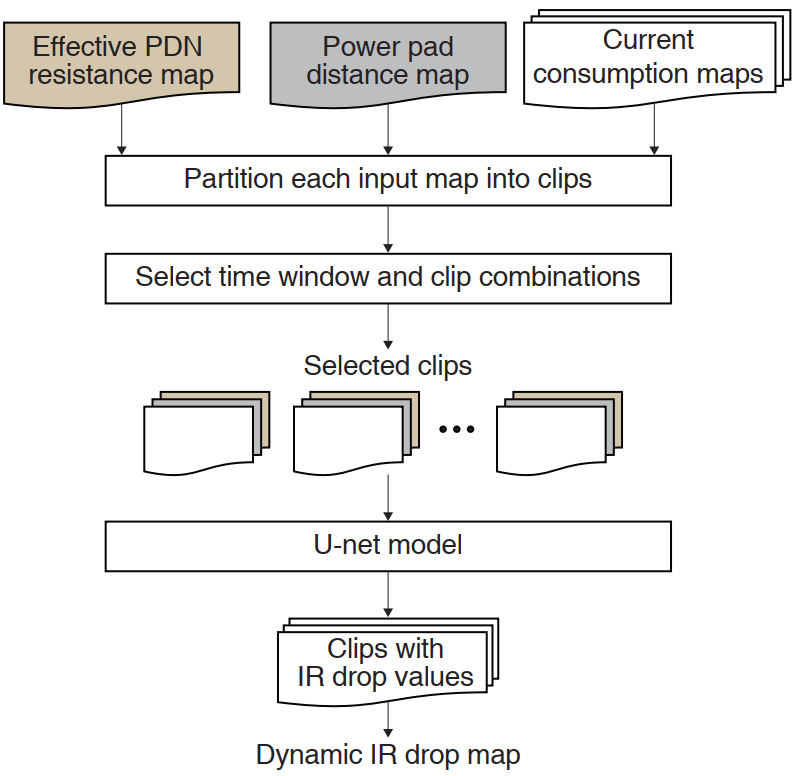

회로의 실제 동작 중에 최대로 발생하는 IR drop인 dynamic IR drop 분석은 매우 오래 걸리는 과정이다. 따라서, 본 연구에서는 이미지–이미지 변환 인공신경망의 일종인 U-net을 이용하여 빠르게 dynamic IR drop 분석을 수행하는 방법을 제안하였다. U-net의 input으로는 각 gate까지의 effective 저항, 각 gate의 시간별 전류 소모량, 가장 가까운 power pad까지의 거리를 각각 map으로 나타낸 이미지 clip이 들어가게 된다. 보다 빠른 IR drop 예측을 위하여 모든 clip을 예측하지 않고 높은 IR drop 발생 가능성이 있는 time window에 대해서만 예측을 수행하며, PDN 저항을 빠르게 근사값으로 구하는 방법을 적용하였다. 실험결과, 제안한 IR drop 예측 방법은 실제 dynamic IR drop 분석방법에 대비하여 약 20배 빠르면서 약 15%의 오차를 보였다.

회로의 실제 동작 중에 최대로 발생하는 IR drop인 dynamic IR drop 분석은 매우 오래 걸리는 과정이다. 따라서, 본 연구에서는 이미지–이미지 변환 인공신경망의 일종인 U-net을 이용하여 빠르게 dynamic IR drop 분석을 수행하는 방법을 제안하였다. U-net의 input으로는 각 gate까지의 effective 저항, 각 gate의 시간별 전류 소모량, 가장 가까운 power pad까지의 거리를 각각 map으로 나타낸 이미지 clip이 들어가게 된다. 보다 빠른 IR drop 예측을 위하여 모든 clip을 예측하지 않고 높은 IR drop 발생 가능성이 있는 time window에 대해서만 예측을 수행하며, PDN 저항을 빠르게 근사값으로 구하는 방법을 적용하였다. 실험결과, 제안한 IR drop 예측 방법은 실제 dynamic IR drop 분석방법에 대비하여 약 20배 빠르면서 약 15%의 오차를 보였다.

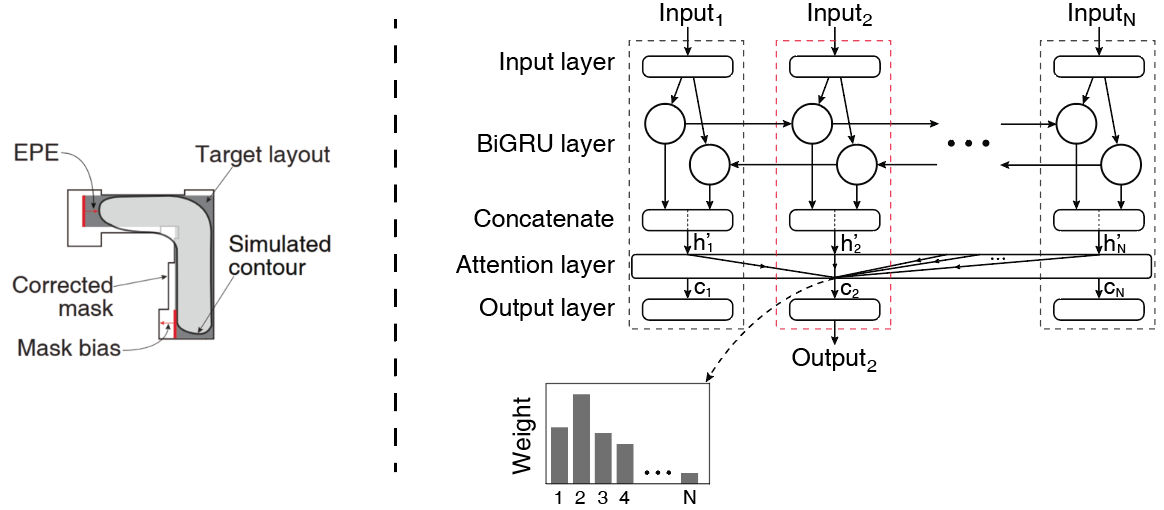

KAIST 신영수 교수 연구팀은 RNN을 이용하여 빠른 OPC를 제안하였다. RNN은 여러 개의 neural network instance가 연속적으로 연결되어 있는데, 이러한 점을 이용하여 RNN을 이용한 OPC에서는 근거리에 있는 여러 개의 segment들의 mask bias를 한번에 예측할 수 있으므로 각각을 개별적으로 예측하는 것에 대비하여 보다 높은 정확도로 OPC를 수행할 수 있다. GRU cell을 양방향으로 연결한 bidirectional GRU 구조를 가지는 RNN을 사용하였으며, RNN의 input, 학습 데이터 sampling, 각 segment와 neural network instance를 효율적으로 mapping하는 방법을 같이 제안하였다. 실험결과, ANN을 사용한 ML-OPC 방법에 대비하여 36% 낮은 EPE를 보여주었다.

빠르고 정확한 리소그래피 시뮬레이션 모델은 OPC나 리소그래피 검증 등에 필수적이다. 이러한 리소그래피 모델은 웨이퍼에 가해지는 빛의 세기를 계산하는 optical 모델과 이를 이용하여 PR의 모양을 결정하는 resist 모델로 이루어져 있다. Resist 모델의 경우 빛의 세기를 map으로 나타낸 이미지와 Gaussian kernel들의 convolution 결과를 weighted sum한 뒤, 이를 특정 threshold와 비교하여 PR의 현상 여부를 결정하는 방식이다. Gaussian과 같은 단순한 모양의 kernel을 이용하기 때문에 정확한 시뮬레이션 결과를 얻기 위해서는 많은 수의 kernel이 필요하고 이에 따라 많은 연산이 필요하게 된다. Resist 모델의 연산 방식이 CNN과 유사한 것에 착안하여 resist 모델을 CNN으로 나타내고, free-form을 가지는 resist kernel들을 CNN을 학습시킴으로써 최적화하였다. 기존에 9개의 Gaussian resist kernel을 사용하던 모델을 2개의 free-form kernel로 대체하였고, 이를 통해 35% 빠른 리소그래피 시뮬레이션 속도와 함께 모델 정확도가 15% 향상되었다.

국문 abstract

빠르고 정확한 리소그래피 시뮬레이션 모델은 OPC나 리소그래피 검증 등에 필수적이다. 이러한 리소그래피 모델은 웨이퍼에 가해지는 빛의 세기를 계산하는 optical 모델과 이를 이용하여 PR의 모양을 결정하는 resist 모델로 이루어져 있다. Resist 모델의 경우 빛의 세기를 map으로 나타낸 이미지와 Gaussian kernel들의 convolution 결과를 weighted sum한 뒤, 이를 특정 threshold와 비교하여 PR의 현상 여부를 결정하는 방식이다. Gaussian과 같은 단순한 모양의 kernel을 이용하기 때문에 정확한 시뮬레이션 결과를 얻기 위해서는 많은 수의 kernel이 필요하고 이에 따라 많은 연산이 필요하게 된다. Resist 모델의 연산 방식이 CNN과 유사한 것에 착안하여 resist 모델을 CNN으로 나타내고, free-form을 가지는 resist kernel들을 CNN을 학습시킴으로써 최적화하였다. 기존에 9개의 Gaussian resist kernel을 사용하던 모델을 2개의 free-form kernel로 대체하였고, 이를 통해 35% 빠른 리소그래피 시뮬레이션 속도와 함께 모델 정확도가 15% 향상되었다.

국문 abstract

회로의 실제 동작 중에 최대로 발생하는 IR drop인 dynamic IR drop 분석은 매우 오래 걸리는 과정이다. 따라서, 본 연구에서는 이미지–이미지 변환 인공신경망의 일종인 U-net을 이용하여 빠르게 dynamic IR drop 분석을 수행하는 방법을 제안하였다. U-net의 input으로는 각 gate까지의 effective 저항, 각 gate의 시간별 전류 소모량, 가장 가까운 power pad까지의 거리를 각각 map으로 나타낸 이미지 clip이 들어가게 된다. 보다 빠른 IR drop 예측을 위하여 모든 clip을 예측하지 않고 높은 IR drop 발생 가능성이 있는 time window에 대해서만 예측을 수행하며, PDN 저항을 빠르게 근사값으로 구하는 방법을 적용하였다. 실험결과, 제안한 IR drop 예측 방법은 실제 dynamic IR drop 분석방법에 대비하여 약 20배 빠르면서 약 15%의 오차를 보였다.

국문 abstract

RNN을 이용하여 빠른 OPC를 제안하였다. RNN은 여러 개의 neural network instance가 연속적으로 연결되어 있는데, 이러한 점을 이용하여 RNN을 이용한 OPC에서는 근거리에 있는 여러 개의 segment들의 mask bias를 한번에 예측할 수 있으므로 각각을 개별적으로 예측하는 것에 대비하여 보다 높은 정확도로 OPC를 수행할 수 있다. GRU cell을 양방향으로 연결한 bidirectional GRU 구조를 가지는 RNN을 사용하였으며, RNN의 input, 학습 데이터 sampling, 각 segment와 neural network instance를 효율적으로 mapping하는 방법을 같이 제안하였다. 실험결과, ANN을 사용한 ML-OPC 방법에 대비하여 36% 낮은 EPE를 보여주었다.

우리 학부 김주영 교수님께서 센터장으로 부임하시는 KAIST ITRC 인공지능반도체시스템(AISS)연구센터가 출범합니다. 2020 대학 ICT연구센터 사업으로 새로이 선정되었으며, 해당 사업은 과기정통부 산하 정보통신기획평가원(IITP)에서 주관하고 있습니다. 김주영 교수님께서는 ‘비대면·인공지능 사회를 위한 반도체 시스템 융합혁신기술 개발’을 목표로 총 50여억원의 연구비로 2025년까지 연구과제를 이끌 계획입니다.

이번 연구센터는 서울, 대전, 울산을 잇는 거점연구센터로 대전에 위치하여 연세대, 이화여대, 울산과기대와 공동 연구를 진행할 예정입니다.

해당 연구센터 개소식이 이번 금요일 오전 10시 30분에 진행될 예정입니다. 이번 개소식은 코로나 바이러스 확산 방지 차원에서 온라인으로 진행될 예정입니다. (https://us02web.zoom.us/j/84476190909 (ZOOM))

우리 학부 박현욱 연구부총장님께서도 연사로 참여를 하시니, 구성원 여러분의 관심 부탁드립니다.

[link]

http://www.aitimes.kr/news/articleView.html?idxno=18666 (전자신문 보도)

우리 학부 유회준 교수님 연구팀이 생성적 적대 신경망(GAN: Generative Adversarial Network)을 저전력, 효율적으로 처리하는 인공지능(AI: Artificial Intelligent) 반도체를 개발하였습니다.

연구팀이 개발한 인공지능 반도체는 다중-심층 신경망을 처리할 수 있고 이를 저전력의 모바일 기기에서도 학습할 수 있습니다. 연구팀은 이번 반도체 칩 개발을 통해 이미지 합성, 스타일 변환, 손상 이미지 복원 등의 생성형 인공지능 기술을 모바일 기기에서 구현하는 데 성공했습니다.

강상훈 박사과정이 1 저자로 참여한 이번 연구결과는 지난 2월 17일 3천여 명 반도체 연구자들이 미국 샌프란시스코에 모여 개최한 국제고체회로설계학회(ISSCC)에서 발표되었습니다. (논문명 : GANPU: A 135TFLOPS/W Multi-DNN Training Processor for GANs with Speculative Dual-Sparsity Exploitation)

최근 모바일 기기에서 인공지능을 구현하기 위해 다양한 가속기 개발이 이뤄지고 있지만, 기존 연구들은 추론 단계만 지원하거나 단일-심층 신경망 학습에 한정되어 있습니다. 연구팀은 단일-심층 신경망뿐만 아니라 생성적 적대 신경망과 같은 다중-심층 신경망을 처리할 수 있으면서 모바일에서 학습도 가능한 인공지능 반도체 GANPU(Generative Adversarial Networks Processing Unit)를 개발해 모바일 장치의 인공지능 활용범위를 넓혔습니다.

연구팀이 개발한 인공지능 반도체는 서버로 데이터를 보내지 않고 모바일 장치 내에서 생성적 적대 신경망(GAN)을 스스로 학습할 수 있어 사생활을 보호를 가능케 하는 프로세서라는 점에서 그 활용도가 기대됩니다. 자체 개발한 기술을 사용함으로써 연구팀의 GANPU는 기존 최고 성능을 보이던 심층 신경망 학습 반도체 대비 4.8배 증가한 에너지효율을 달성했습니다.

연구팀은 GANPU의 활용 예시로 태블릿 카메라로 찍은 사진을 사용자가 직접 수정할 수 있는 응용 기술을 시연했습니다. 사진상의 얼굴에서 머리·안경·눈썹 등 17가지 특징에 대해 추가·삭제 및 수정사항을 입력하면 GANPU가 실시간으로 이를 자동으로 완성해 보여 주는 얼굴 수정 시스템을 개발했습니다.

[Link]

https://www.ytn.co.kr/_ln/0115_202004070308303992

https://news.kaist.ac.kr/news/html/news/?mode=V&mng_no=6831

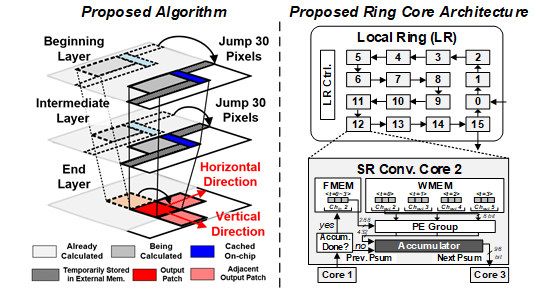

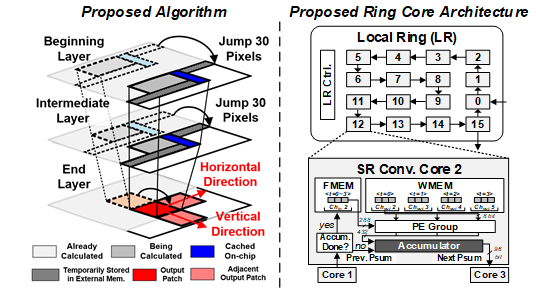

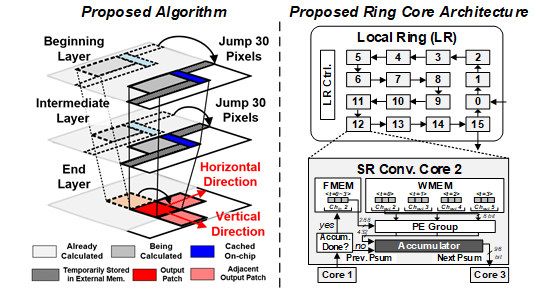

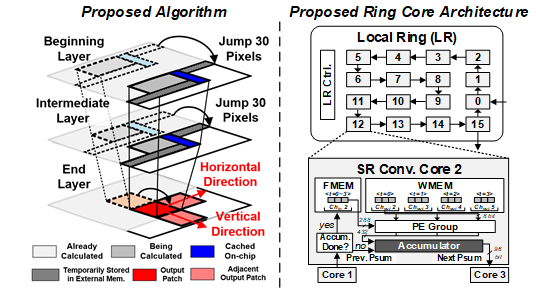

Title: A Full HD 60 fps CNN Super Resolution Processor with Selective Caching based Layer Fusion for Mobile Devices

Authors: Ju-Hyoung Lee, Dong-Joo Shin, Jin-Su Lee, Jin-Mook Lee, Sang-Hoon Kang, and Hoi-Jun Yoo

Recently, super resolution algorithms based on convolution neural network (SR-CNN) has been broadly utilized to enable mobile devices to support better user experience (UX) from video quality enhancement or far object recognition. However, SRCNN’s distinct architecture makes it harder to meet the high throughput requirement in conventional hardware targeting classification CNNs. It is because the intermediate feature maps of SR do not decrease when they pass through the layers, while classification CNN’s feature maps shrink due to pooling or strided convolutions. Because of the huge amount of feature maps in SR-CNN, it requires larger external memory access (EMA), on-chip memory footprint and computation workload than the classification CNN.

In this work, we propose a high throughput SR-CNN processor which minimizes the amount of EMA and on-chip memory footprint with three key features; 1) Selective caching based layer fusion (SCLF) algorithm to reduce the overall memory cost (product of on-chip memory size and EMA), 2) memory compaction scheme to reduce the on-chip memory footprint further and 3) cyclic ring core architecture to increase the PE utilization for SCLF. As a result, the implemented processor achieves 60 frames-per-second throughput in generating full HD images.

Figure 1. An illustration of the proposed SR computing algorithm & proposed ring core architecture