Minki Jeong, Wanyeong Jung, “MAC-DO: DRAM-Based Multi-Bit Analog Accelerator Using Output Stationary,” IEEE International Symposium on Circuits and Systems (ISCAS), 2024

Abstract: DRAM-based accelerators have shown their potential in addressing the memory wall challenge of the traditional von Neumann architecture. Such accelerators exploit charge sharing or logic circuits for simple logic operations. As a result, they require many cycles for more complex operations such as a multi-bit multiply-accumulate (MAC) operation, resulting in significant data access and movement and potentially worsening power efficiency.

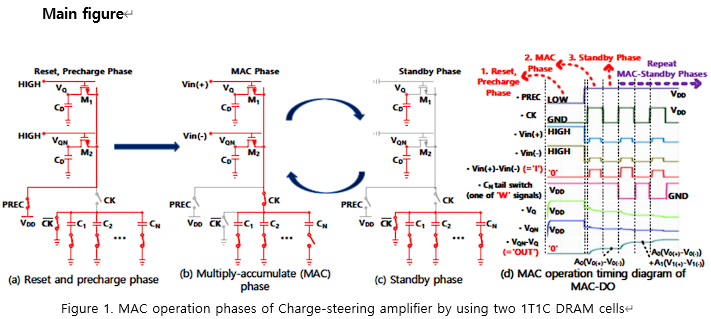

To overcome these limitations, this paper presents MAC-DO, an efficient and low-power DRAM-based accelerator. Compared to previous DRAM-based accelerators, a MAC-DO cell, consisting of two 1T1C DRAM cells, innately supports a multi-bit MAC operation within a single cycle, significantly improving power efficiency while maintaining good linearity and compatibility with existing 1T1C DRAM cell and array structures. This achievement is facilitated by a novel analog computation method utilizing charge steering. As a result, MAC-DO efficiently can accelerate convolutions based on output stationary mapping, supporting the majority of computations performed in deep neural networks.

Our evaluation using transistor-level simulation shows that a test MAC-DO array with 16×16 MAC-DO cells achieves 120.96 TOPS/W and 97.07% Top-1 accuracy for MNIST dataset without retraining.