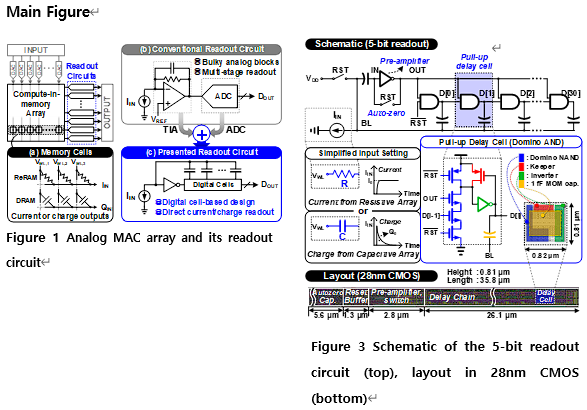

Minkyu Yang, Changjoo Park, Wanyeong Jung, “A Compact and Low-Power Column Readout Circuit based on Digital Delay Chain“, IEEE International Symposium on Circuits and Systems (ISCAS), 2024

Abstract: This paper presents a column readout integrated circuit (ROIC) optimized for analog compute-in-memory (CIM) arrays in AI applications in terms of size, design simplicity, robustness, and energy efficiency. The digital delay chain with capacitive feedback converts current and charge input to a thermometer code with high accuracy. Adopting dynamic AND gates allows for sequentially changing the negative feedback loop through unit capacitors controlled by a loop-unrolled chain topology. The readout circuit shows superior linearity with essentially no stability problems. Simulated with a 28 nm CMOS technology, the circuit achieves a 5-bit resolution with a DNL of +1.148/-1.147 LSB and an INL of +0.817/-0.677 LSB in the case of current input for 3σ mismatch. The power consumption is 54.8 µW from a 0.9 V supply at the conversion rate of 400 MS/s, and the circuit occupies 29 µm2.