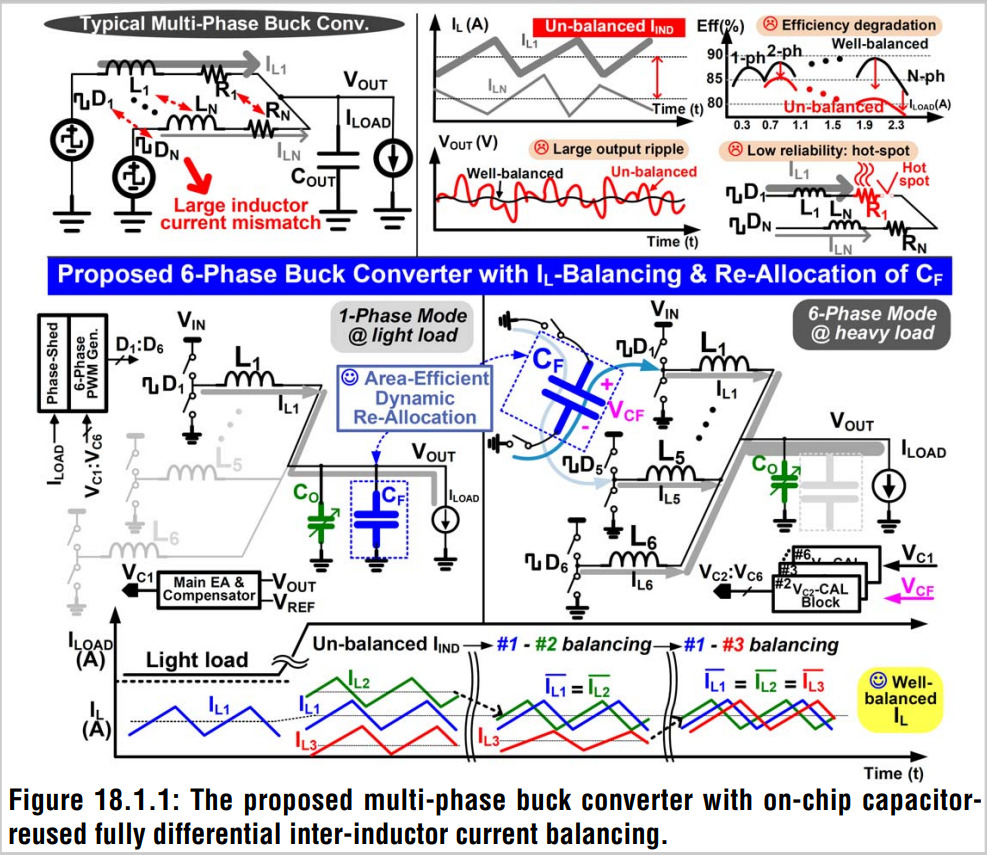

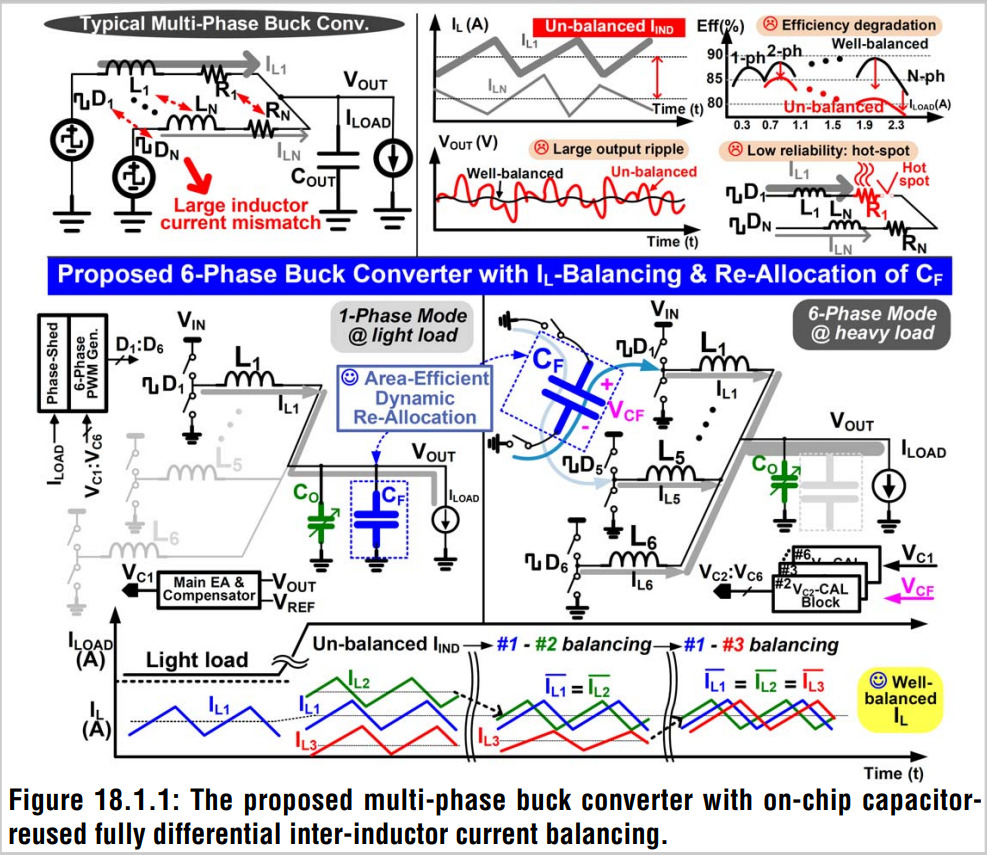

This paper presents a 400MHz 6-phase buck converter with bond-wire inductors. Peak-and-valley differential sensing, which is realized with a reused on-chip capacitor, corrects inter-inductor current imbalance without power overhead. Owing to dynamic re-allocation of on-chip capacitors, transient response can be accelerated with constrained ripple. The chip fabricated in 28-nm achieved the state-of-the-art power density of 1.23W/mm2 and DVS rate of 75mV/ns. Peak efficiency of 83.7% was measured.

Title : An Overview of Processing-in-Memory Circuits for Artificial Intelligence and Machine Learning

Authors : Donghyuk Kim, Chengshuo Yu, Shanshan Xie, Yuzong Chen, Joo-Young Kim, Bongjin Kim, Jaydeep Kulkarni, Tony Tae-Hyoung Kim

Publications : IEEE Journal on Emerging and Selected Topics in Circuits and Systems (JETCAS), 2022

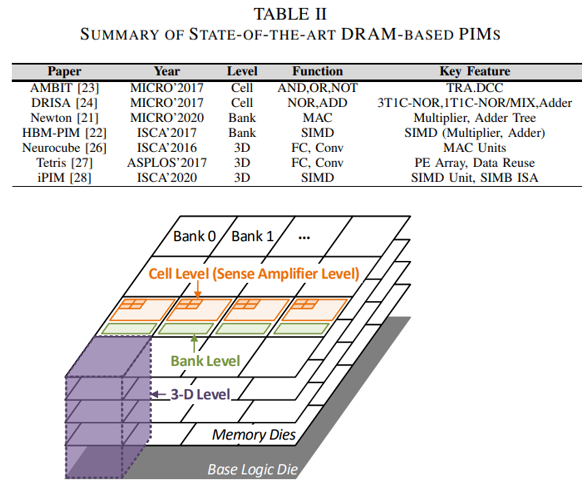

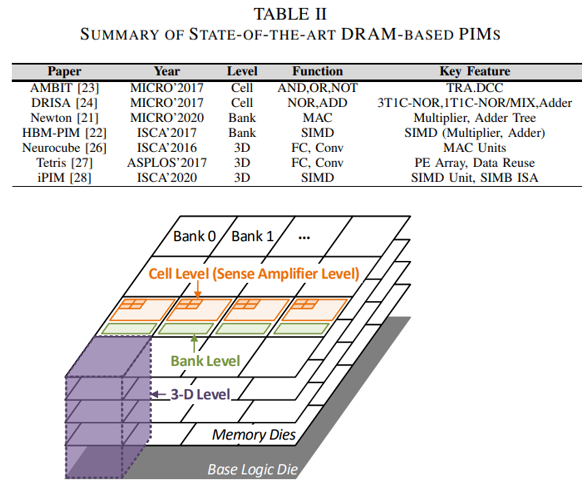

Artificial intelligence (AI) and machine learning (ML) are revolutionizing many fields of study, such as visual recognition, natural language processing, autonomous vehicles, and prediction. Traditional von-Neumann computing architecture with separated processing elements and memory devices have been improving their computing performances rapidly with the scaling of process technology. However, in the era of AI and ML, data transfer between memory devices and processing elements becomes the bottleneck of the system. To address this data movement issue, memory-centric computing takes an approach of merging the memory devices with processing elements so that computations can be done in the same location without moving any data. Processing-In-Memory (PIM) has attracted research community’s attention because it can improve the energy efficiency of memory-centric computing systems substantially by minimizing the data movement. Even though the benefits of PIM are well accepted, its limitations and challenges have not been investigated thoroughly. This paper presents a comprehensive investigation of state-of-the-art PIM research works based on various memory device types, such as static-random-access-memory (SRAM), dynamic-random-access-memory (DRAM), and resistive memory (ReRAM). We will present the overview of PIM designs in each memory type, covering from bit cells, circuits, and architecture. Then, a new software stack standard and its challenges for incorporating PIM with the conventional computing architecture will be discussed. Finally, we will discuss various future research directions in PIM for further reducing the data conversion overhead, improving

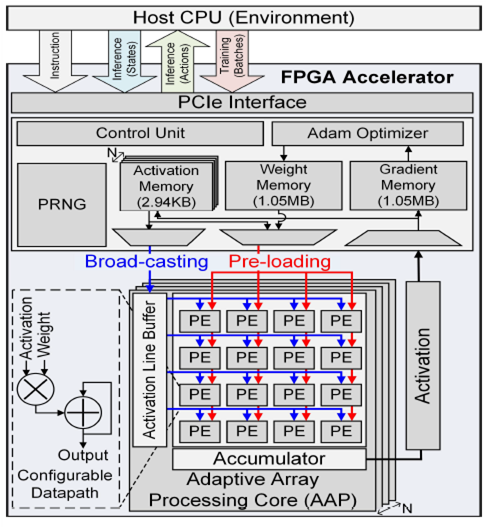

Deep reinforcement learning (DRL) is a powerful technology to deal with decision-making problem in various application domains such as robotics and gaming, by allowing an agent to learn its action policy in an environment to maximize a cumulative reward. Unlike supervised models which actively use data quantization, DRL still uses the single-precision floating-point for training accuracy while it suffers from computationally intensive deep neural network (DNN) computations.

In this paper, we present a deep reinforcement learning acceleration platform named FIXAR, which employs fixed-point data types and arithmetic units for the first time using a SW/HW co-design approach. We propose a quantization-aware training algorithm in fixed-point, which enables to reduce the data precision by half after a certain amount of training time without losing accuracy. We also design a FPGA accelerator that employs adaptive dataflow and parallelism to handle both inference and training operations. Its processing element has configurable datapath to efficiently support the proposed quantized-aware training. We validate our FIXAR platform, where the host CPU emulates the DRL environment and the FPGA accelerates the agent’s DNN operations, by running multiple benchmarks in continuous action spaces based on a latest DRL algorithm called DDPG. Finally, the FIXAR platform achieves 25293.3 inferences per second (IPS) training throughput, which is 2.7 times higher than the CPU-GPU platform. In addition, its FPGA accelerator shows 53826.8 IPS and 2638.0 IPS/W energy efficiency, which are 5.5 times higher and 15.4 times more energy efficient than those of GPU, respectively. FIXAR also shows the best IPS throughput and energy efficiency among other state-of-the-art acceleration platforms using FPGA, even it targets one of the most complex DNN models.

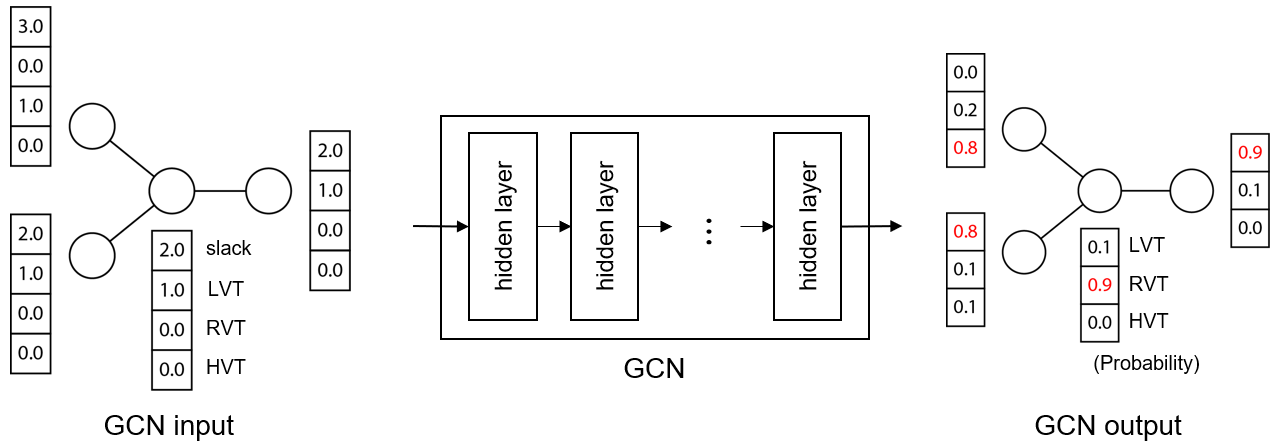

회로 설계 마지막 단계에서 더 적은 누설전류를 가지는 cell (e.g. 더 높은 Vth 혹은 더 긴 gate 길이를 가지는 cell)로 바꾸는 engineering change order (ECO)는 과정을 통해 회로의 소비 전력을 줄일 수 있다. 하지만 이 과정은 cell을 swapping하는것과 cell들의 timing을 검증하는 과정이 반복적으로 수행되기 때문에 오랜 시간이 소요된다. 본 논문에서는 graph convolutional network (GCN)을 적용하여 빠른 ECO를 수행하는 것을 제안한다. GCN은 cell들간의 연결관계와 timing 정보를 통해 Vth를 예측하고 평균적으로 83%의 정확도로 Vth를 정확하게 예측하였다. 또한, minimum implant width (MIW)를 고려한 timing violation fix를 위하여 heuristic한 Vth 재배정 방법을 제안하였다. 이를 통하여 누설전류의 52% 감소 (기존 ECO의 경우 61% 감소)와 기존 ECO방법 대비 두배 이상 빠른 ECO를 수행하였다.

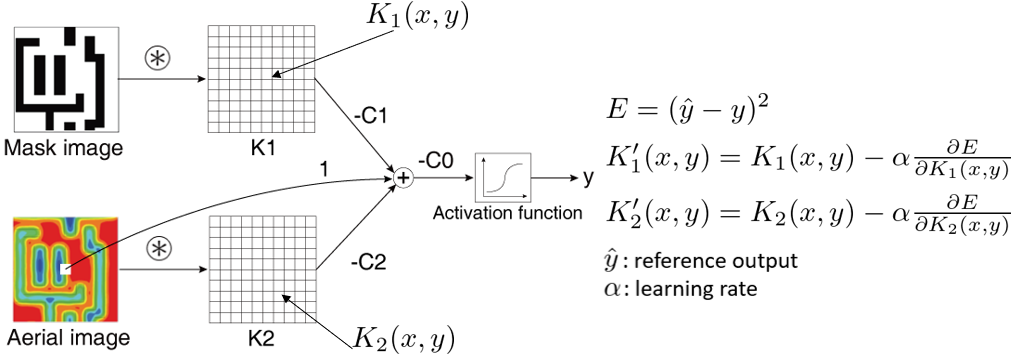

빠르고 정확한 리소그래피 시뮬레이션 모델은 OPC나 리소그래피 검증 등에 필수적이다. 이러한 리소그래피 모델은 웨이퍼에 가해지는 빛의 세기를 계산하는 optical 모델과 이를 이용하여 PR의 모양을 결정하는 resist 모델로 이루어져 있다. Resist 모델의 경우 빛의 세기를 map으로 나타낸 이미지와 Gaussian kernel들의 convolution 결과를 weighted sum한 뒤, 이를 특정 threshold와 비교하여 PR의 현상 여부를 결정하는 방식이다. Gaussian과 같은 단순한 모양의 kernel을 이용하기 때문에 정확한 시뮬레이션 결과를 얻기 위해서는 많은 수의 kernel이 필요하고 이에 따라 많은 연산이 필요하게 된다. Resist 모델의 연산 방식이 CNN과 유사한 것에 착안하여 resist 모델을 CNN으로 나타내고, free-form을 가지는 resist kernel들을 CNN을 학습시킴으로써 최적화하였다. 기존에 9개의 Gaussian resist kernel을 사용하던 모델을 2개의 free-form kernel로 대체하였고, 이를 통해 35% 빠른 리소그래피 시뮬레이션 속도와 함께 모델 정확도가 15% 향상되었다.

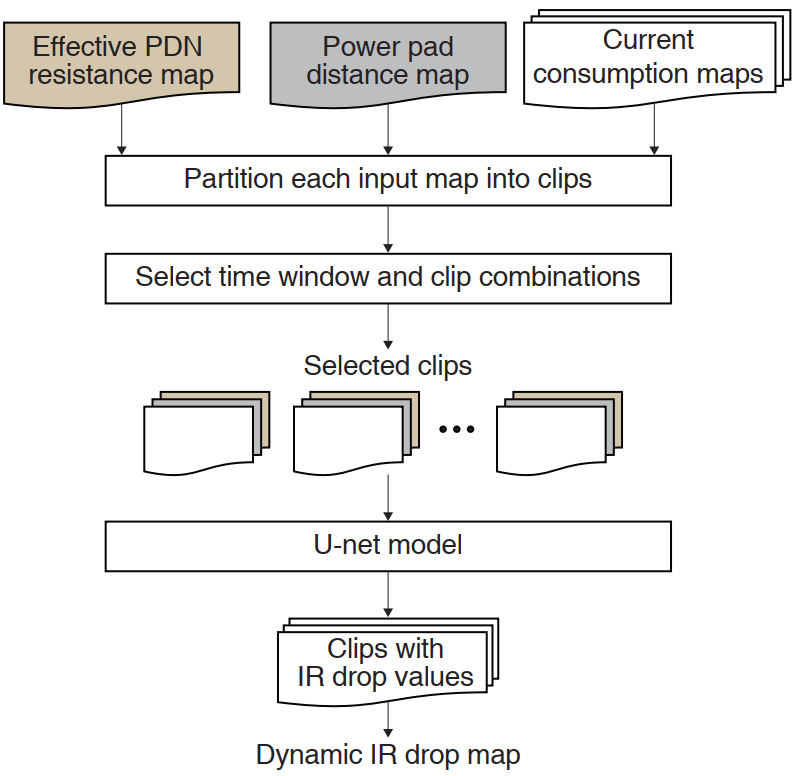

회로의 실제 동작 중에 최대로 발생하는 IR drop인 dynamic IR drop 분석은 매우 오래 걸리는 과정이다. 따라서, 본 연구에서는 이미지–이미지 변환 인공신경망의 일종인 U-net을 이용하여 빠르게 dynamic IR drop 분석을 수행하는 방법을 제안하였다. U-net의 input으로는 각 gate까지의 effective 저항, 각 gate의 시간별 전류 소모량, 가장 가까운 power pad까지의 거리를 각각 map으로 나타낸 이미지 clip이 들어가게 된다. 보다 빠른 IR drop 예측을 위하여 모든 clip을 예측하지 않고 높은 IR drop 발생 가능성이 있는 time window에 대해서만 예측을 수행하며, PDN 저항을 빠르게 근사값으로 구하는 방법을 적용하였다. 실험결과, 제안한 IR drop 예측 방법은 실제 dynamic IR drop 분석방법에 대비하여 약 20배 빠르면서 약 15%의 오차를 보였다.

회로의 실제 동작 중에 최대로 발생하는 IR drop인 dynamic IR drop 분석은 매우 오래 걸리는 과정이다. 따라서, 본 연구에서는 이미지–이미지 변환 인공신경망의 일종인 U-net을 이용하여 빠르게 dynamic IR drop 분석을 수행하는 방법을 제안하였다. U-net의 input으로는 각 gate까지의 effective 저항, 각 gate의 시간별 전류 소모량, 가장 가까운 power pad까지의 거리를 각각 map으로 나타낸 이미지 clip이 들어가게 된다. 보다 빠른 IR drop 예측을 위하여 모든 clip을 예측하지 않고 높은 IR drop 발생 가능성이 있는 time window에 대해서만 예측을 수행하며, PDN 저항을 빠르게 근사값으로 구하는 방법을 적용하였다. 실험결과, 제안한 IR drop 예측 방법은 실제 dynamic IR drop 분석방법에 대비하여 약 20배 빠르면서 약 15%의 오차를 보였다.

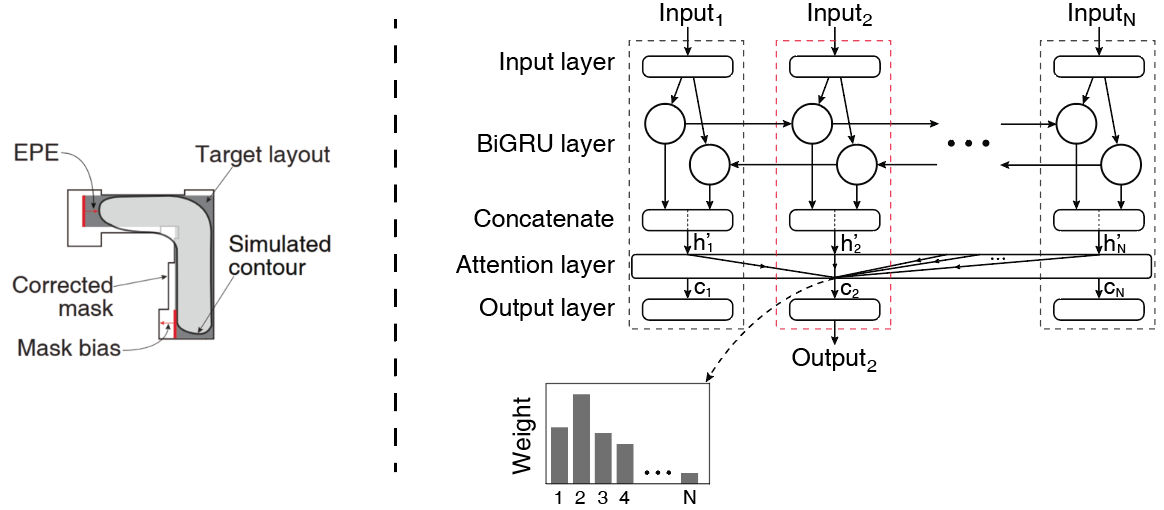

KAIST 신영수 교수 연구팀은 RNN을 이용하여 빠른 OPC를 제안하였다. RNN은 여러 개의 neural network instance가 연속적으로 연결되어 있는데, 이러한 점을 이용하여 RNN을 이용한 OPC에서는 근거리에 있는 여러 개의 segment들의 mask bias를 한번에 예측할 수 있으므로 각각을 개별적으로 예측하는 것에 대비하여 보다 높은 정확도로 OPC를 수행할 수 있다. GRU cell을 양방향으로 연결한 bidirectional GRU 구조를 가지는 RNN을 사용하였으며, RNN의 input, 학습 데이터 sampling, 각 segment와 neural network instance를 효율적으로 mapping하는 방법을 같이 제안하였다. 실험결과, ANN을 사용한 ML-OPC 방법에 대비하여 36% 낮은 EPE를 보여주었다.

빠르고 정확한 리소그래피 시뮬레이션 모델은 OPC나 리소그래피 검증 등에 필수적이다. 이러한 리소그래피 모델은 웨이퍼에 가해지는 빛의 세기를 계산하는 optical 모델과 이를 이용하여 PR의 모양을 결정하는 resist 모델로 이루어져 있다. Resist 모델의 경우 빛의 세기를 map으로 나타낸 이미지와 Gaussian kernel들의 convolution 결과를 weighted sum한 뒤, 이를 특정 threshold와 비교하여 PR의 현상 여부를 결정하는 방식이다. Gaussian과 같은 단순한 모양의 kernel을 이용하기 때문에 정확한 시뮬레이션 결과를 얻기 위해서는 많은 수의 kernel이 필요하고 이에 따라 많은 연산이 필요하게 된다. Resist 모델의 연산 방식이 CNN과 유사한 것에 착안하여 resist 모델을 CNN으로 나타내고, free-form을 가지는 resist kernel들을 CNN을 학습시킴으로써 최적화하였다. 기존에 9개의 Gaussian resist kernel을 사용하던 모델을 2개의 free-form kernel로 대체하였고, 이를 통해 35% 빠른 리소그래피 시뮬레이션 속도와 함께 모델 정확도가 15% 향상되었다.

국문 abstract

빠르고 정확한 리소그래피 시뮬레이션 모델은 OPC나 리소그래피 검증 등에 필수적이다. 이러한 리소그래피 모델은 웨이퍼에 가해지는 빛의 세기를 계산하는 optical 모델과 이를 이용하여 PR의 모양을 결정하는 resist 모델로 이루어져 있다. Resist 모델의 경우 빛의 세기를 map으로 나타낸 이미지와 Gaussian kernel들의 convolution 결과를 weighted sum한 뒤, 이를 특정 threshold와 비교하여 PR의 현상 여부를 결정하는 방식이다. Gaussian과 같은 단순한 모양의 kernel을 이용하기 때문에 정확한 시뮬레이션 결과를 얻기 위해서는 많은 수의 kernel이 필요하고 이에 따라 많은 연산이 필요하게 된다. Resist 모델의 연산 방식이 CNN과 유사한 것에 착안하여 resist 모델을 CNN으로 나타내고, free-form을 가지는 resist kernel들을 CNN을 학습시킴으로써 최적화하였다. 기존에 9개의 Gaussian resist kernel을 사용하던 모델을 2개의 free-form kernel로 대체하였고, 이를 통해 35% 빠른 리소그래피 시뮬레이션 속도와 함께 모델 정확도가 15% 향상되었다.