Hyungjoon Bae, Da Won Kim, Wanyeong Jung, “VVIP: Versatile Vertical Indexing Processor for Edge Computing,” ACM/IEEE Design Automation Conference (DAC), 2024

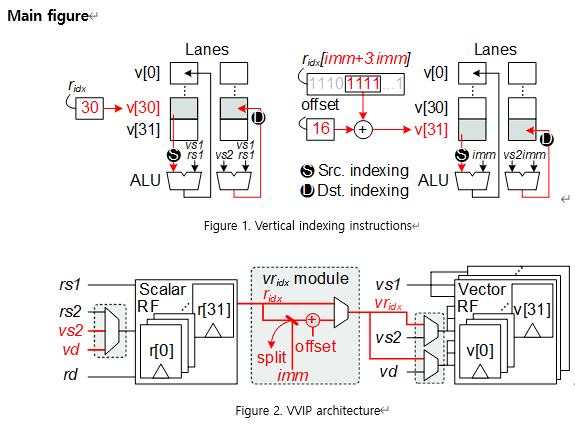

Abstract: This paper presents a versatile vertical indexing processor (VVIP) based on a single-instruction multiple-data architecture for edge computing. In VVIP, the vertical source and destination indexing instructions are customized for area-efficient computations. The proposed indexing method reorders data within a processing module by using more registers and data-steering logic in the calculations. In particular, VVIP supports multibit-serial multiplication and sparse data operations by leveraging register files as lookup tables or accumulators. The VVIP, verified on a vector processor, has an area overhead of less than 2.8%. It exhibits an average computation rate that is 10.1 times faster than the 1-bit-serial multiplication in linear algebra benchmark s, and 1.2 times average performance improvement in unstructured sparse point-wise convolution tasks when compared to conventional control sequences.

s, and 1.2 times average performance improvement in unstructured sparse point-wise convolution tasks when compared to conventional control sequences.