다양한 분야에서 높은 정확성을 얻기 위해 딥러닝 모델 및 데이터셋의 규모가 빠르게 증가하고 있다. 하지만 대규모 심층 신경망 (DNN) 모델을 훈련하려면 엄청난 양의 계산과 메모리가 필요하며, 따라서 대규모 DNN 모델을 훈련하기위한 병렬화 기술이 주목받고 있다. 대규모 DNN 모델을 병렬화하기 위한 여러 접근 방식이 제안되었지만 이러한 방식은 통신 시간이 길고 작업자 메모리가 제한되어 확장성이 부족하다. 기존 방식들은 통신 시간을 줄이기 위해 정확도를 희생하기도 한다.

이 연구에서 우리는 정확도 손실없이 훈련 시간을 최소화하기 위해 그룹 하이브리드 병렬 처리 (GHP)라는 효율적인 병렬 처리 기법을 제안한다. 두 가지 핵심 아이디어로 접근하였다. 첫째, 작업자를 그룹화하고 그룹별로 교육하면 작업자 간의 불필요한 커뮤니케이션 오버 헤드가 줄어든다. 이를 통해 대규모 네트워크 훈련 과정에서 엄청난 양의 네트워크 리소스를 절약한다. 둘째, 데이터와 모델 병렬 처리를 혼합하면 통신 시간을 줄이고 작업자 메모리 문제를 완화한다. 데이터와 모델 병렬화는 서로 보완 적이므로 결합시 훈련 시간을 향상시킬 수 있다. 데이터의 학습 시간 모델을 수학적으로 제시하였으며, 모델 병렬화와 학습 시간 모델을 기반으로 학습 시간 최소화를위한 병렬화 방법을 결정하는 휴리스틱을 제안한다.

제안하는 그룹 하이브리드 병렬 처리 기법이 처리량 측면에서 다른 기법들을 능가하는 결과를 얻어 정확도 손실 없이 학습을 가속화함을 확인하였다.

abstract

흔히 드론이라고 불리는 로터리형 무인 비행체는 비행 거리의 제한 때문에 아직도 그 실제 활용에 한계를 가지고 있지만 하드웨어의 향상에 의한 비행거리의 증가는 이미 한계에 다다른 상태이다. 이 논문은 electronic design automation (EDA) 의 framework 를 끼반으로 한 시스템적인 드론의 저전력 최적화 방법을 소개한다.

우리는 드론의 유체역학, 제어역학 적 이해 없이 기계학습과 드론의 간단한 물리적 파라미터 (삼축 속도, 가속도, 높이, 무게 및 볼륨, 그리고 바람의 영향 등) 를 이용하여 파워 모델링을 소개하고, 디테일한 실험방법, 성능 검증, 그리고 에너지 최적 경로 형성을 위한 최적화 과정을 제시한다.

그 결과, 우리는 실제 비행의 약 90 %의 정확도에 달하는 파워 모델링을 제작하였고, 외력을 고려한 실질적인 무인 비행기의 경로 최적화를 진행하였다. 제안한 방법은 약 24.01% 의 에너지 절약 효과를 보인다.

초록

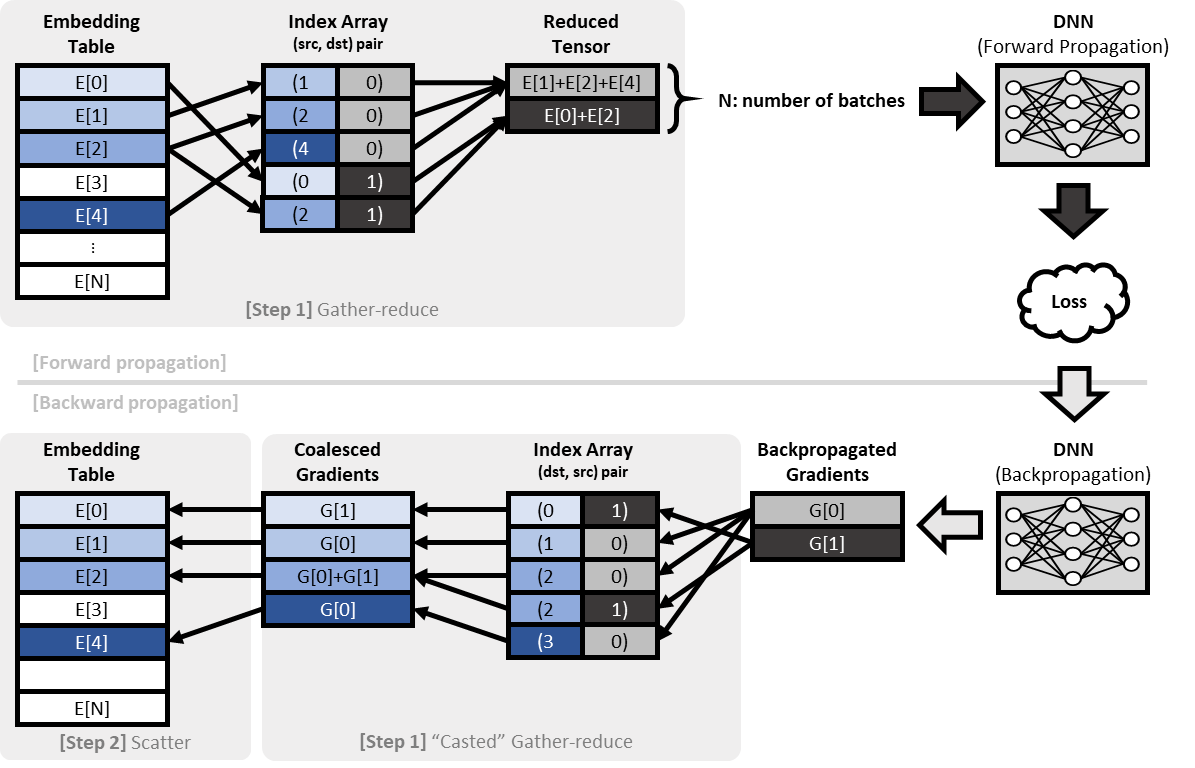

클라우드 데이터센터에서 가장 널리 사용되는 인공지능 워크로드는 개인 맞춤형 추천 서비스이다. 근래에는 이와 같은 중요성에 입각하여 인공지능 기반의 추천 서비스의 추론 과정 가속을 위한 고성능 아키텍처 연구가 발표되고 있으나, 아직 이와 같은 추천 인공지능의 학습에 대한 연구는 미비한 상태이다. 본 논문에서는 추천 인공지능 학습과정에 대한 상세한 분석을 통해 희소 임베딩 레이어의 학습과정이 주된 병목을 야기함을 밝혀내었으며, 이를 해결하기 위한 텐서 캐스팅 기법을 개발하였다. 텐서 캐스팅 기법은 임베딩 레이어 학습을 위한 모든 핵심연산을 취합-환산 연산으로 단일화하는 방법을 제공함으로써 임베딩 레이어 학습을 위한 범용적 가속기 아키텍처 설계를 가능하게 하였다. 실제 CPU-GPU 시스템에서 작동하는 프로토타입에서의 실험 결과 텐서 캐스팅 기법을 통해 기존 시스템 대비 1.9-15배의 학습 성능 향상을 얻을 수 있었다.

초록

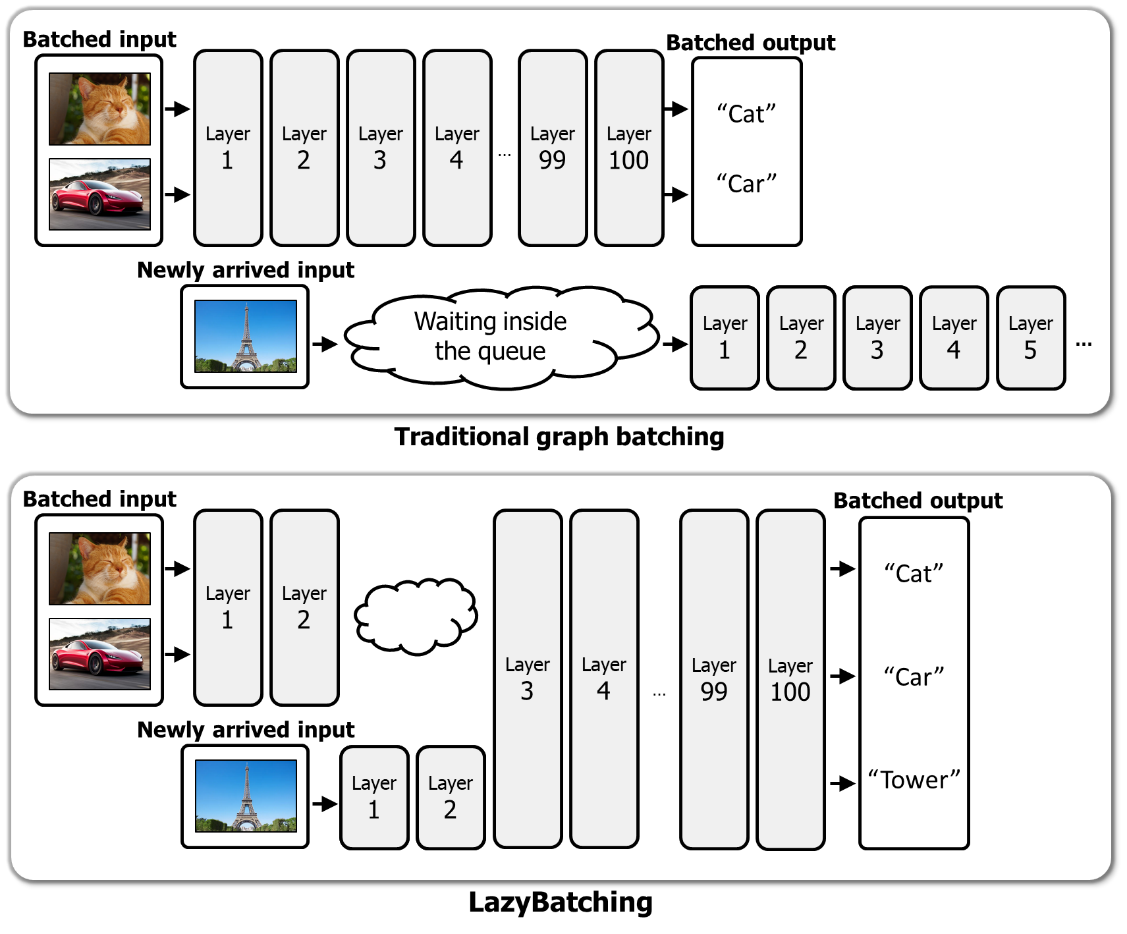

클라우드 인공지능 추론 시스템에서 배칭은 연산 처리량을 늘리고 총소유비용을 절감할 수 있도록 하는 필수적인 기술이다. 기존 추론 서버에서 활용하는 그래프 단위의 배칭은 다수의 사용자 데이터에 대한 추론 연산을 전체 인공지능 그래프 단위로 동시에 실행한다. 본 연구진은 이러한 전체 그래프 단위의 배칭은 동적인 연산 요청을 처리가 요구되는 인공지능 추론 상황에서 심각한 연산 비효율을 야기하여 성능을 극대화하지 못한다는 문제점을 발견하였다. 이에 본 연구진은 그래프 단위의 수행에서 벗어나 개별 레이어 단위로 유동적인 배칭을 가능하게 하는 레이지 배칭을 제안한다. 레이지 배칭은 개별 레이어 단위로 여러 입력을 동시에 실행할 수 있는 고도화된 알고리즘을 통해 기존 배칭 방법을 개선한다. 레이지 배칭은 기존 추론 서버의 배칭 방법 대비 평균응답시간, 처리량, 서비스수준규약 만족 정도를 각각 평균 15배, 1.5배, 5.5배 향상시킨다.

저자 : 정찬영, 이승욱, 성현기, 안드레아 피나치, 심현철

Workshop: IEEE ICRA 2021 : Opportunities and challenges with autonomous racing [Best paper award]

Link : https://linklab-uva.github.io/icra-autonomous-racing/

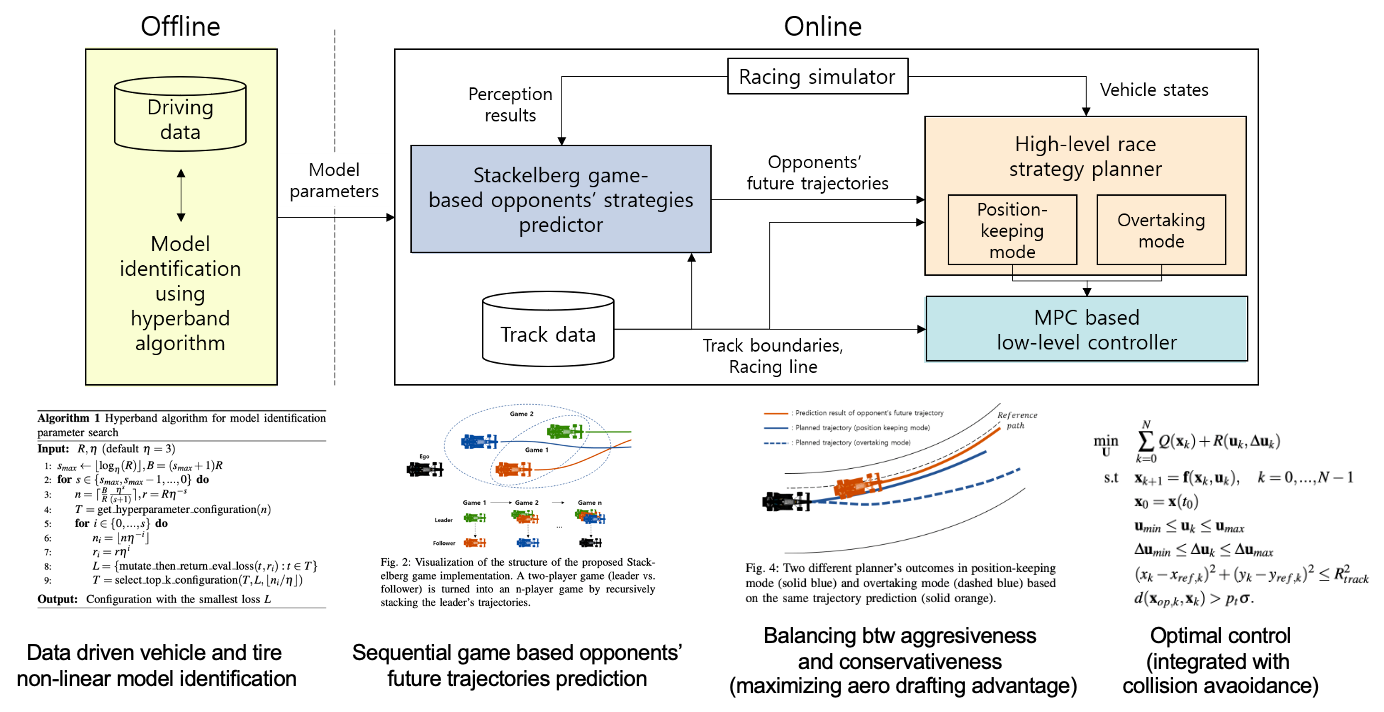

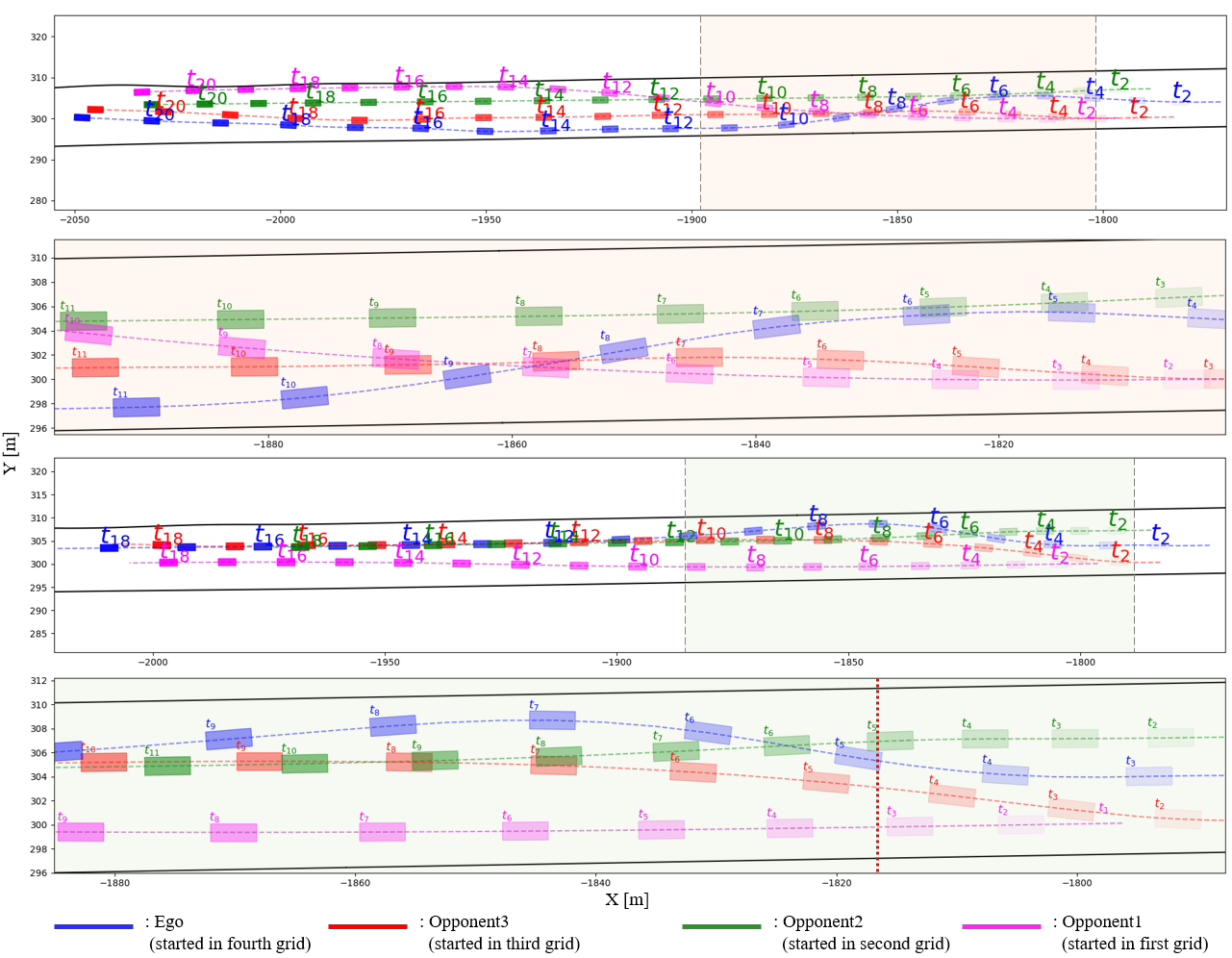

자율 주행의 특수한 상황에서의 어려움을 해결하기 위해, 다대다 자율 주행 레이싱은 학계 및 산업계에서 많은 관심을 받고 있다. 본 연구에서는 다대다 자율 주행 레이싱을 위한 게임 이론 기반 모델 예측 제어 방법과 데이터 기반 차량 모델 식별법을 제안한다. 제안하는 제어기는 1) 게임 이론 기반 주변 차량 예측, 2) 레이싱 전략 계획 3)모델 예측 기반 차량 제어기로 구성되어있다. 제안하는 방법론은 Indy Autonomous Challenge의 공식 시뮬레이터의 다양한 레이싱 시나리오에서 검증되었다. 제안하는 방법을 통해 우리의 방법은 레이싱 트렉을 빠르게 주행하면서도 주변 차량을 충돌없이 추월할 수 있음을 실험적으로 검증하였다.

그림1. 다대다 자율 레이싱을 위한 방법론 시각화

그림2. Head-to-head simulation racing results

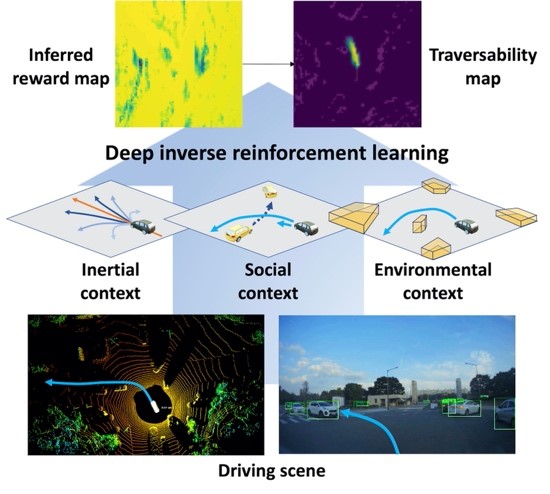

주변 물체가 존재하는 환경에서의 자율 주행은 여전히 어려운 문제이다. 주요 기술적 어려움은 내적, 환경적, 사회적 컨텍스트를 고려하여 확률적으로 근미래 궤적을 표현하는 주행 가능 맵을 정확하게 예측하는 것이다. 이를 해결하기 위해 다양한 방법들이 제안되어왔다. 하지만 기존 연구들은 대부분 개별적인 컨텍스트를 반영하는 것에 집중하였다. 또한 대부분의 기존 연구들에서는 HD맵과 같은 값비산 사전 정보를 입력으로 사용하여 방법의 확장성을 제한하였다.

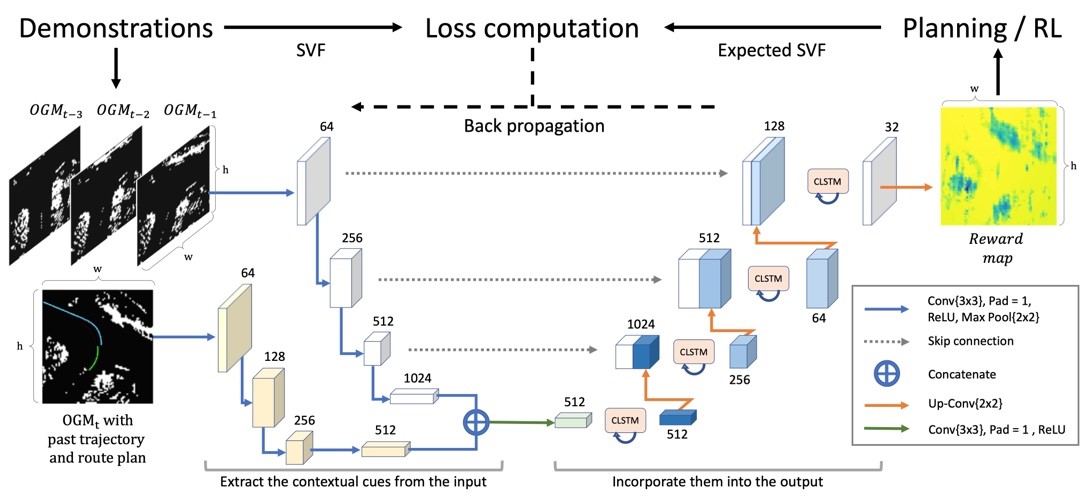

본 연구에서는 동적 환경에서 자율 주행을 위한 다중 컨텍스트가 반영된 주행 가능 맵 예측이 가능한 역강화 학습 기법을 제안하였다. 주행 환경의 사전 정보를 사용하는 대신, 우리는 실시간으로 입력되는 센서로부터 다양한 컨텍스트를 추출하고, 이를 최종 출력인 보상 맵에 반영하는 딥뉴럴 네트워크를 제안한다. 우리의 방법은 현재 자신의 위치로부터 확률적으로 주행 가능한 맵을 보상 맵으로 부터 유추한다.

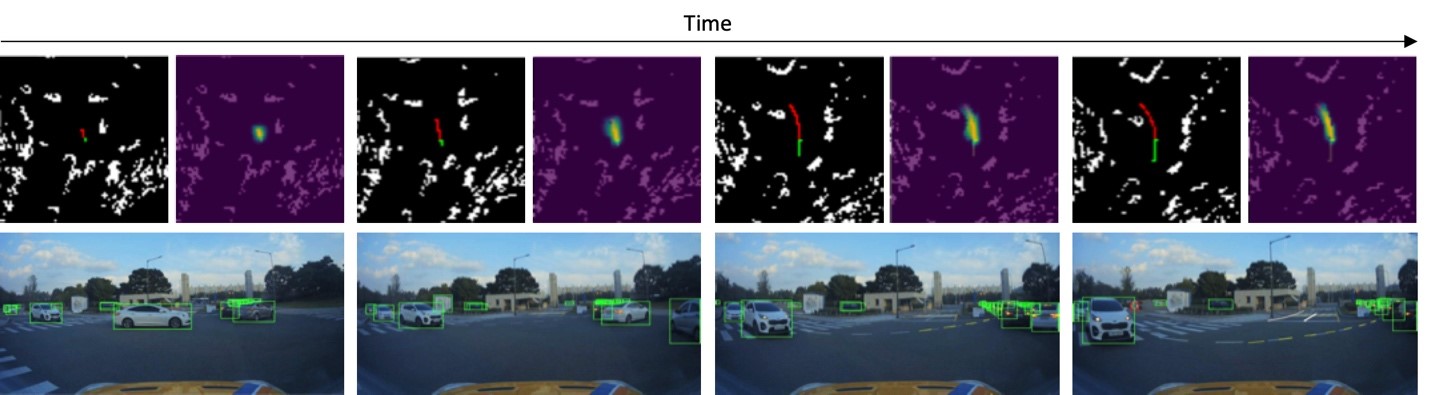

제안된 방법은 실제 교통 데이터를 바탕으로 다양한 베이스라인과 함께 양적, 질적으로 검증되었다. 실험 결과는 다른 방법들에 비해 정확한 예측 정확도를 보였고, 실제 운전자와도 유사한 경로를 예측하는 것으로 확인되었다.

그림1. 역강화 학습을 이용한 다중 컨텍스트가 반영된 주행 가능 맵 예측 방법

그림2 . 제안하는 네트워크 아키텍쳐 시각화 결과

그림3. 시간에 따른 주행 가능 지도 가시화 결과

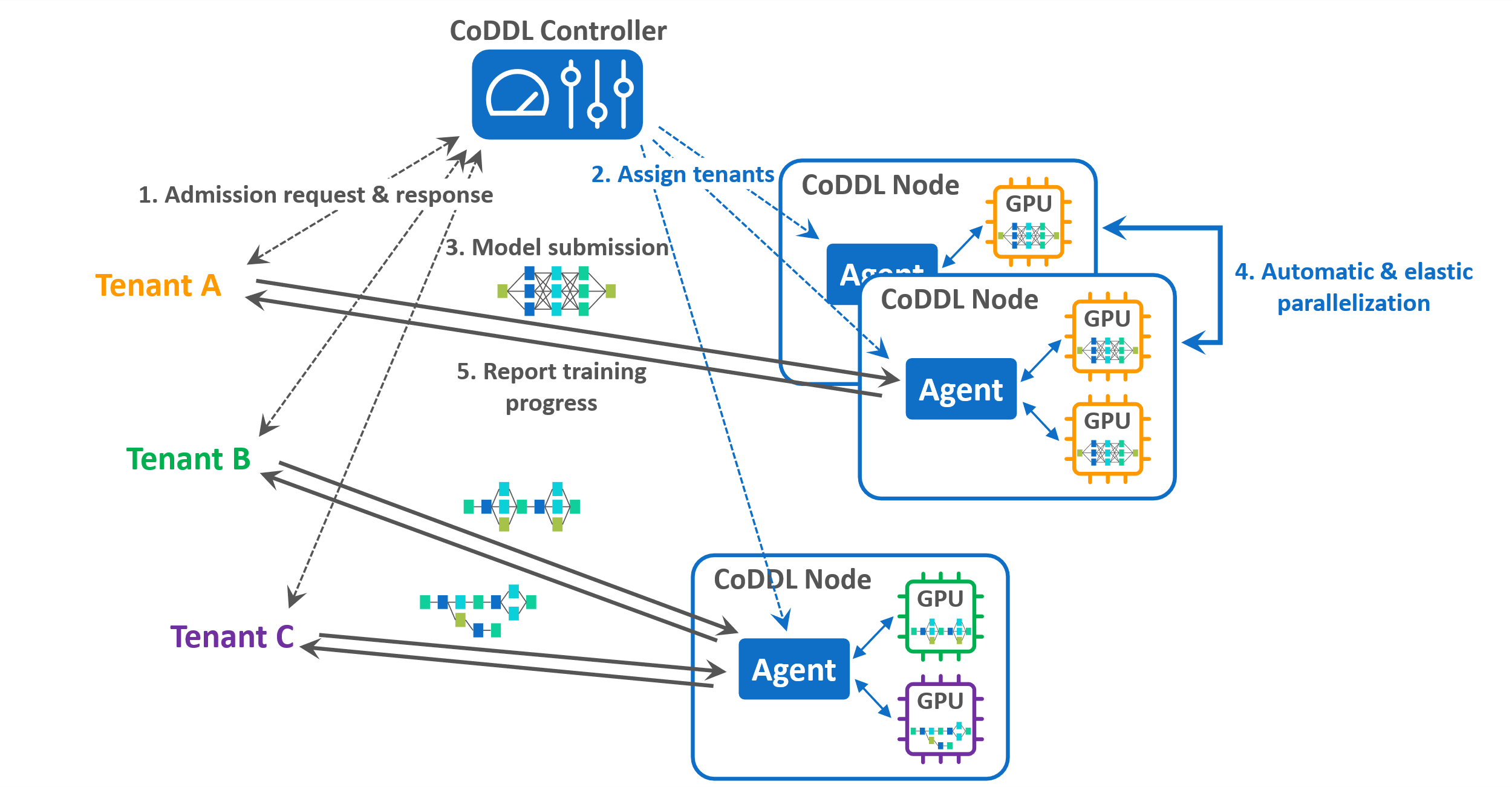

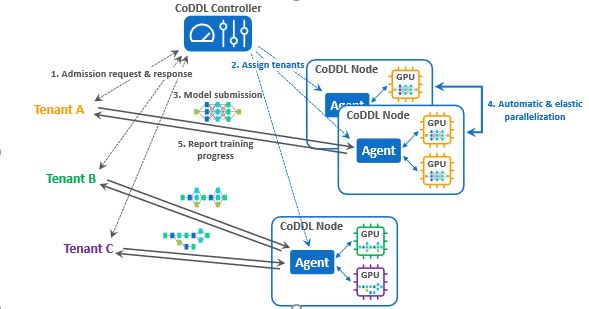

우리 학부 황창호, 김태현 박사과정 연구원이 (박경수 (지도교수), 신진우 교수, MIT CSAIL 김승현 학생 공동연구) 인공지능 학습을 가속하기 위한 고성능 GPU 클러스터 자원 관리 프레임워크인 CoDDL 시스템을 개발하였습니다. 본 시스템은 한국전자통신연구원 (ETRI)과의 협력하에 개발되었습니다.

인공지능 모델을 학습하기 위한 GPU 자원의 수요가 폭발적으로 늘어남에 따라, 많은 기업들 및 클라우드 컴퓨팅 사업자들은 각자의 GPU 클러스터를 구축하고 인공지능 개발자들에게 GPU를 분배하여 학습 연산에 활용할 수 있도록 지원하고 있습니다. 이러한 GPU 클러스터는 구축하는데 높은 초기비용이 들 뿐 아니라 매우 많은 전력을 소모하기 때문에, 클러스터의 GPU 자원을 효율적으로 관리하기 위한 시스템을 구현하는 것이 더욱 중요해지고 있습니다.

본 연구팀이 개발한 CoDDL 시스템은 인공지능 개발자들이 구현한 모델이 GPU 클러스터 내에서 빠르고 효율적으로 학습되도록 자동으로 관리해주는 시스템입니다. 개발자들이 학습시키고자 하는 모델을 시스템에 제출하면, 모델이 여러 GPU를 동시에 활용하여 고속 학습되도록 자동으로 병렬화 해주며, 특히 학습이 진행되는 도중에도 클러스터의 전체적인 성능을 최적화하기 위해 각 학습 작업이 사용하는 GPU 개수를 탄력적으로 변경하는 작업 스케줄러가 구현되어 있습니다. CoDDL 시스템은 각 학습 작업에 할당된 GPU 개수를 변경하는데 소요되는 시간을 최소화함으로써 작업 스케줄러가 더욱 효율적이고 정교한 자원 배분을 할 수 있도록 하고, 따라서 전체적인 학습 속도를 크게 높일 수 있습니다.

본 연구에서 제안한 AFS-P 스케줄러는 마이크로소프트가 공개한 인공지능 학습용 GPU 클러스터 트레이스에서 기존 최고 스케줄러 대비 최대 3.11배 빠른 평균 작업 완료 시간 (average job completion time)을 보였으며, 본 성과는 네트워크 컴퓨터 시스템 분야 최고 권위 학회 중 하나인 USENIX NSDI 2021에서 발표되었습니다.

그림: CoDDL 시스템 개요

자세한 연구 내용은 하단의 링크에서 확인하실 수 있습니다.

논문: https://www.usenix.org/system/files/nsdi21-hwang.pdf

학회 발표 영상: https://www.usenix.org/conference/nsdi21/presentation/hwang

우리 학부 황창호, 김태현 박사과정 연구원이 (박경수 (지도교수), 신진우 교수, MIT CSAIL 김승현 학생 공동연구) 인공지능 학습을 가속하기 위한 고성능 GPU 클러스터 자원 관리 프레임워크인 CoDDL 시스템을 개발하였습니다. 본 시스템은 한국전자통신연구원 (ETRI)과의 협력하에 개발되었습니다.

인공지능 모델을 학습하기 위한 GPU 자원의 수요가 폭발적으로 늘어남에 따라, 많은 기업들 및 클라우드 컴퓨팅 사업자들은 각자의 GPU 클러스터를 구축하고 인공지능 개발자들에게 GPU를 분배하여 학습 연산에 활용할 수 있도록 지원하고 있습니다. 이러한 GPU 클러스터는 구축하는데 높은 초기비용이 들 뿐 아니라 매우 많은 전력을 소모하기 때문에, 클러스터의 GPU 자원을 효율적으로 관리하기 위한 시스템을 구현하는 것이 더욱 중요해지고 있습니다.

본 연구팀이 개발한 CoDDL 시스템은 인공지능 개발자들이 구현한 모델이 GPU 클러스터 내에서 빠르고 효율적으로 학습되도록 자동으로 관리해주는 시스템입니다. 개발자들이 학습시키고자 하는 모델을 시스템에 제출하면, 모델이 여러 GPU를 동시에 활용하여 고속 학습되도록 자동으로 병렬화 해주며, 특히 학습이 진행되는 도중에도 클러스터의 전체적인 성능을 최적화하기 위해 각 학습 작업이 사용하는 GPU 개수를 탄력적으로 변경하는 작업 스케줄러가 구현되어 있습니다. CoDDL 시스템은 각 학습 작업에 할당된 GPU 개수를 변경하는데 소요되는 시간을 최소화함으로써 작업 스케줄러가 더욱 효율적이고 정교한 자원 배분을 할 수 있도록 하고, 따라서 전체적인 학습 속도를 크게 높일 수 있습니다.

본 연구에서 제안한 AFS-P 스케줄러는 마이크로소프트가 공개한 인공지능 학습용 GPU 클러스터 트레이스에서 기존 최고 스케줄러 대비 최대 3.11배 빠른 평균 작업 완료 시간 (average job completion time)을 보였으며, 본 성과는 네트워크 컴퓨터 시스템 분야 최고 권위 학회 중 하나인 USENIX NSDI 2021에서 발표되었습니다.

그림: CoDDL 시스템 개요

자세한 연구 내용은 하단의 링크에서 확인하실 수 있습니다.

논문: https://www.usenix.org/system/files/nsdi21-hwang.pdf

학회 발표 영상: https://www.usenix.org/conference/nsdi21/presentation/hwang

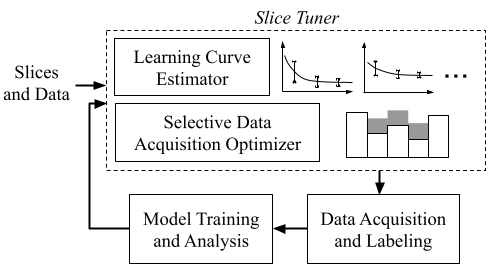

전기및전자공학부 황의종 교수님 연구실 태기현 박사과정생이 정확하고 공정한 머신러닝 모델을 위한 선택적 데이터 수집 기법을 개발했습니다.

머신러닝이 현대 사회에 폭넓게 사용되면서 책임 있는 인공지능의 필요성이 대두되고 있습니다. 높은 정확도를 넘어서 책임 있는 인공지능의 목표에는 공정성(fairness), 강건성(robustness), 설명가능성(explainability) 등이 포함되어 있습니다. 특히, Google, Microsoft, IBM 등의 회사에서 책임있는 인공지능을 강조하고 있습니다.

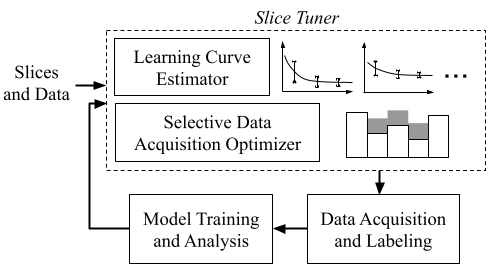

본 연구에서는 인공지능 공정성에 초점을 맞추고 불공정한 인공지능의 근원이 편향된 훈련 데이터에 있다는 점에 착안하여, 데이터 수집 단계에서부터 인공지능 모델의 정확도와 공정성을 함께 고려한 프레임워크인 Slice Tuner를 제안하였습니다. Slice Tuner는 데이터양에 따라 모델의 손실을 추정할 수 있는 학습 곡선(learning curve)을 효율적이고 신뢰할 수 있도록 관리하고, 이를 활용하여 정확하고 공정한 모델을 위한 최적의 데이터 수집 방법을 제시합니다.

연구팀은 해당 기술이 데이터 수집단계에서 부터 책임 있는 인공지능을 실현하기 위한 중요한 첫 단추가 될 수 있다고 설명했습니다. 또한, 본 연구 성과는 데이터베이스 최고 권위 학회인 ACM SIGMOD (International Conference on Management of Data) 2021 에서 발표되었습니다.

자세한 연구 내용은 하단의 링크에서 확인하실 수 있습니다.

Figure 1. Slice Tuner architecture

[논문 정보]

논문명: Slice Tuner: A Selective Data Acquisition Framework for Accurate and Fair Machine Learning Models

저자: 태기현, 황의종(지도교수)

논문 링크: https://arxiv.org/abs/2003.04549

논문 슬라이드: https://docs.google.com/presentation/d/1thnn2rEvTtcCbJc8s3TnHQ2IEDBsZOe66-o-u4Wb3y8/edit?usp=sharing

학회 발표 영상: https://youtu.be/QYEhURcd4u4?list=PL3xUNnH4TdbsfndCMn02BqAAgGB0z7cwq

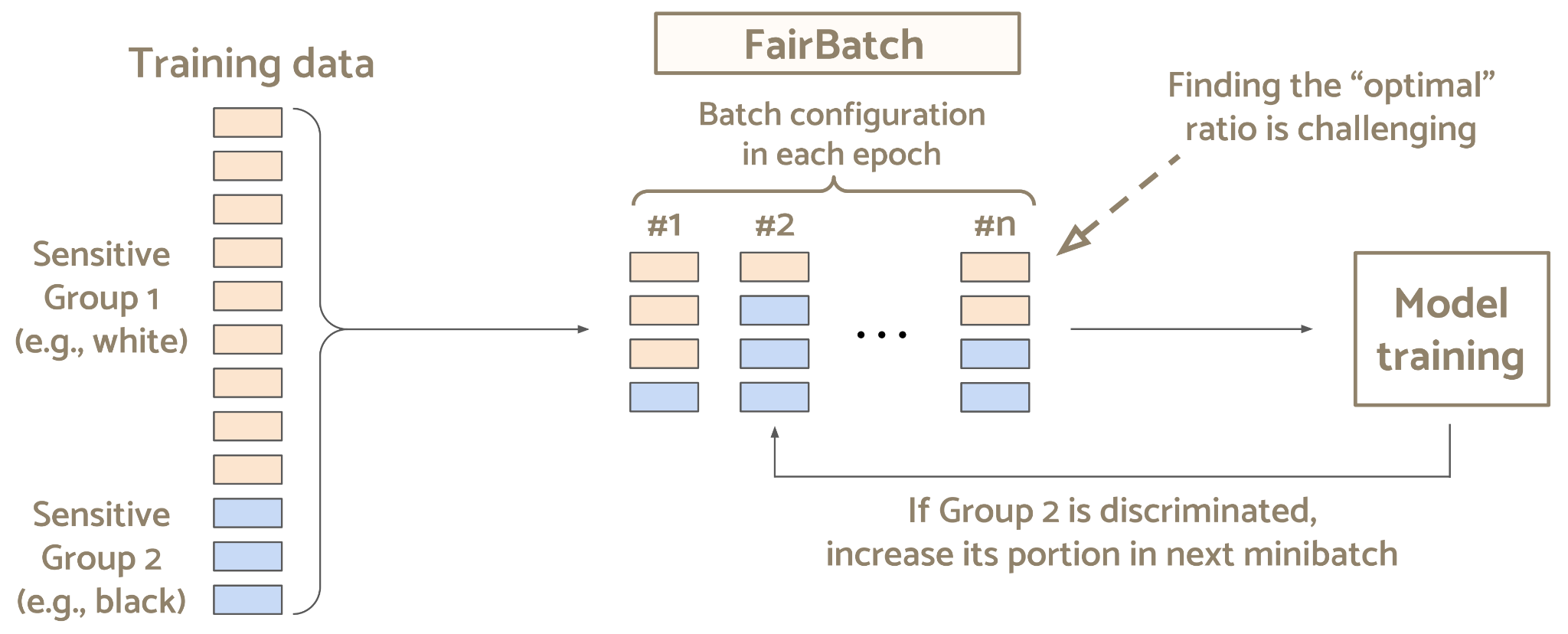

전기및전자공학부 황의종 교수님과 서창호 교수님 연구팀에서 공정한 머신러닝 모델 학습을 위한 새로운 배치 선택 기법을 개발했습니다. 본 연구는 노유지 박사과정(지도교수 황의종)이 주저자로 참여했고, 위스콘신 매디슨 전기컴퓨터공학부 이강욱 교수님과의 공동 연구로 진행되었습니다.

인공지능 기술이 인간에게 단순히 편리성을 가져다주던 단계에서, 이제는 사회 전반에 걸쳐 광범위하게 활용되며 인간의 삶에 많은 영향을 미치고 있습니다. 최근 인공지능의 긍정적인 효과 이면에 머신러닝 모델이 특정 개인 혹은 집단을 차별하는 사례가 다수 발견되었고, 이에 따라 공정성(fairness)을 고려한 머신러닝 학습의 필요성에 대한 사회적인 공감이 커지고 있습니다.

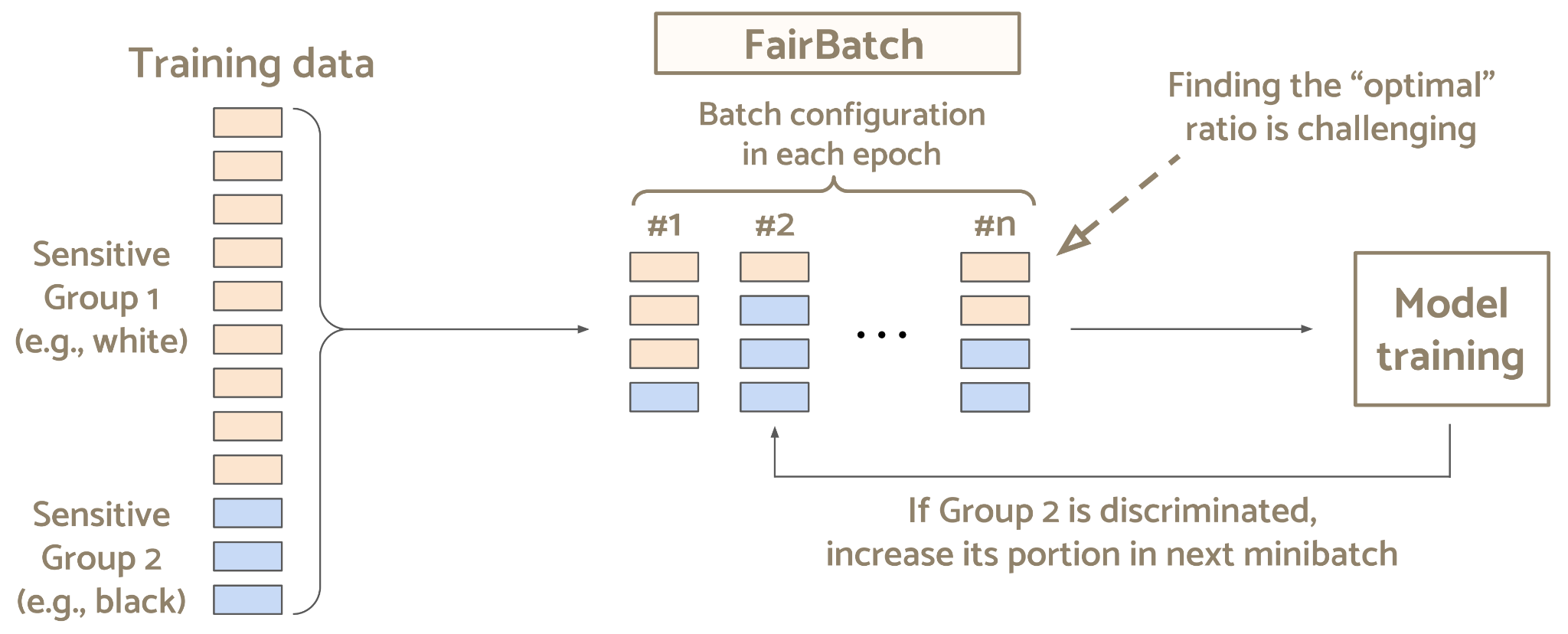

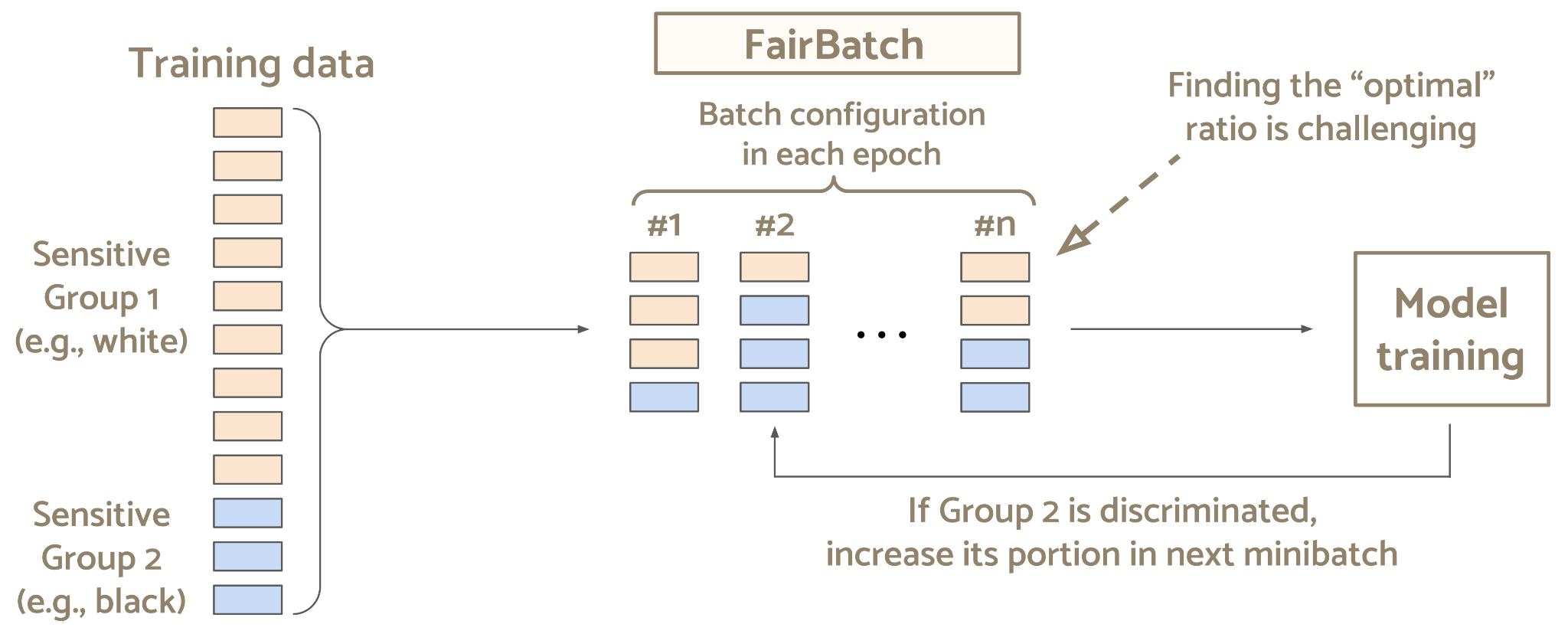

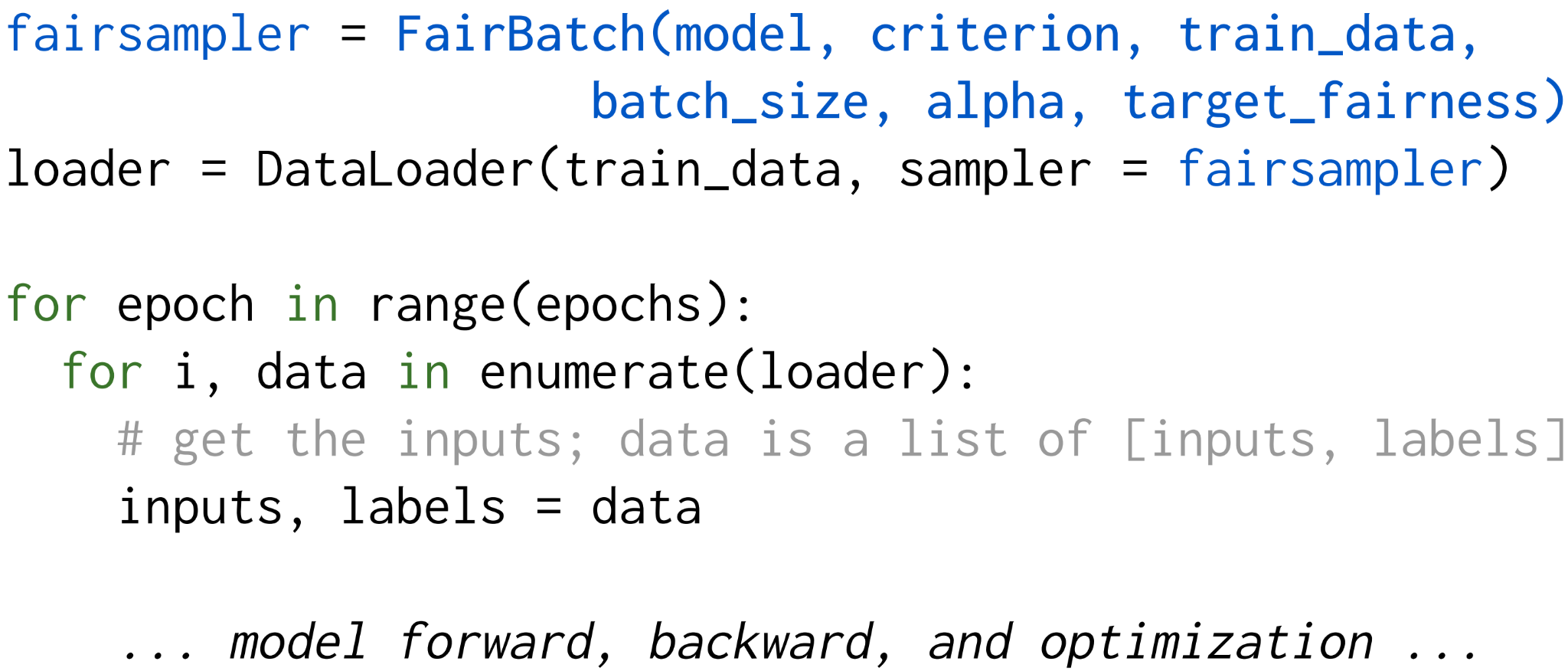

본 연구팀은 공정한 머신러닝 모델 학습을 위한 새로운 배치 선택(batch selection) 기법인 FairBatch를 제안합니다. 기존의 공정성을 위한 머신러닝 기법들은 학습 데이터 혹은 알고리즘 자체에 큰 수정이 요구되었는데, 이와는 달리 FairBatch는 데이터를 샘플링하는 배치 선택 단계에서 한 줄의 코드 변경만으로 높은 정확도와 공정성을 효과적으로 달성합니다. 또한 FairBatch는 이중수준 최적화를 통한 해석을 기반으로 하며, 다양한 시나리오에서 폭 넓게 활용이 가능함을 보였습니다.

연구팀은 FairBatch가 높은 성능을 달성함과 동시에 실제 머신러닝 파이프라인에 쉽게 적용될 수 있다는 장점을 가졌기에, 해당 학습 기법을 다양한 어플리케이션에 적용할 수 있을 것이라고 설명했습니다. 또한 공정한 머신러닝 시스템에 대한 사회적 요구가 더욱 커짐에 따라, 이에 대한 활발한 후속 연구가 진행될 것으로 예상됩니다. 본 연구 성과는 머신러닝 최고 권위 학회인 ICLR (International Conference for Learning Representations) 2021에서 발표되었습니다.

자세한 연구 내용은 하단의 링크에서 확인하실 수 있습니다.

Figure 1. A scenario that shows how FairBatch adaptively adjusts batch ratios in model training for fairness.

Figure 2. PyTorch code for model training where FairBatch is used for batch selection. Only a single-line code change is required to replace an existing sampler with FairBatch, marked in blue.

[Paper information and links]

Title: FairBatch: Batch Selection for Model Fairness

Authors: Yuji Roh (KAIST EE), Kangwook Lee (Wisconsin-Madison Electrical & Computer Engineering), Steven Euijong Whang (KAIST EE), and Changho Suh (KAIST EE)

Paper: https://openreview.net/forum?id=YNnpaAKeCfx

Source code: https://github.com/yuji-roh/fairbatch

Slides: https://docs.google.com/presentation/d/1IfaYovisZUYxyofhdrgTYzHGXIwixK9EyoAsoE1YX-w/edit?usp=sharing