A research article authored by Byung Chul Jang (KAIST EE), Sang Yoon Yang (KAIST EE), Hyejeong Seong (KAIST CBE), Sung Kyu Kim (KAIST MSE), Junhwan Choi (KAIST CBE), Sung Gap Im (KAIST CBE), and Sung-Yool Choi (KAIST EE; Corresponding author) was published at Nano Research (2017.07)

Article title: Zero-static-power nonvolatile logic-in-memory circuits for flexible electronics

Flexible logic circuits and memory with ultra-low static power consumption are in great demand for battery-powered flexible electronic systems. Here, we show that a flexible nonvolatile logic-in-memory circuit enabling normally-off computing can be implemented using a poly(1,3,5-trivinyl-1,3,5-trimethyl cyclotrisiloxane) (pV3D3)-based memristor array. Although memristive logic-in-memory circuits have been previously reported, the requirements of additional components and the large variation of memristors have limited demonstrations to simple gates within a few operation cycles on rigid substrates only. Using memristor-aided logic (MAGIC) architecture requiring only memristors and pV3D3-memristor with good uniformity on a flexible substrate, for the first time, we experimentally demonstrated our implementation of MAGIC-NOT and -NOR gates during multiple cycles and even under bent conditions. Other functions, such as OR, AND, NAND, and a half adder, are also realized by combinations of NOT and NOR gates within a crossbar array. This research advances the development of novel computing architecture with zero static power consumption for battery-powered flexible electronic systems.

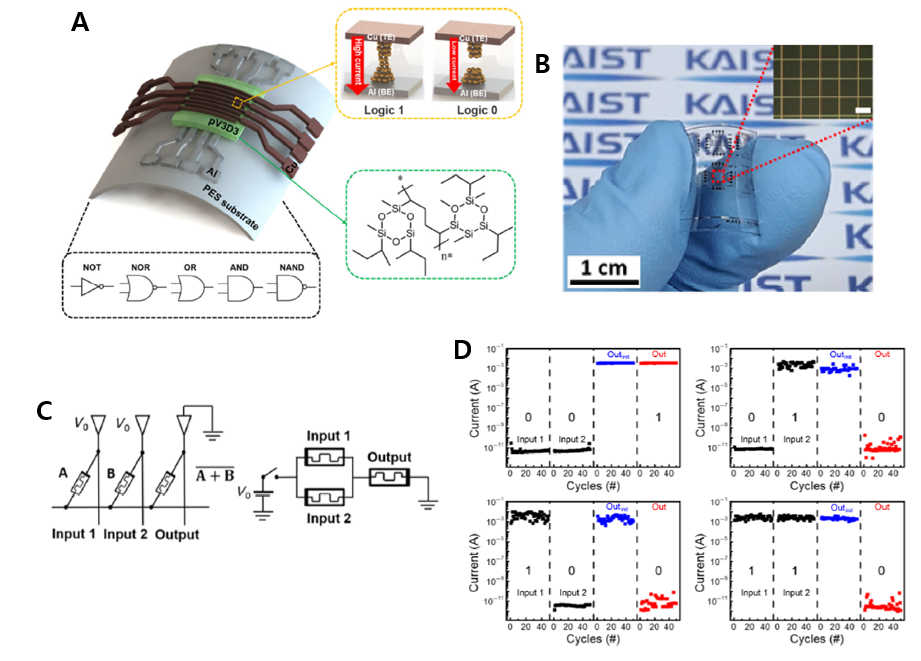

Figure 1. A Schematic illustration of a pV3D3-memristor with an 8 × 8 crossbar array on a plastic substrate. The inset with the orange dotted line shows the logical states of the pV3D3-memristor, the inset with the green dotted line shows the molecular structure of pV3D3, and the inset with the black dotted line depicts the feasible logic gates using the pV3D3-memristor. B Photograph of a flexible pV3D3-memristor on a PES substrate. The inset shows a magnified optical image of the flexible pV3D3-memristor array (scale bar: 20 μm). C MAGIC-NOR gate within the crossbar array and its equivalent circuit. D Experimental results of the MAGIC-NOR gate for all input memristor combinations during 50 cycles.