to be the world’s

top IT powerhouse.We thrive to be the world’s top IT powerhouse.

Our mission is to lead innovations

in information technology, create lasting impact,

and educate next-generation leaders of the world.

- 1

- 6

to be the world’s

top IT powerhouse.We thrive to be the world’s top IT powerhouse.

Our mission is to lead innovations

in information technology, create lasting impact,

and educate next-generation leaders of the world.

- 2

- 6

to be the world’s

top IT powerhouse.We thrive to be the world’s top IT powerhouse.

Our mission is to lead innovations

in information technology, create lasting impact,

and educate next-generation leaders of the world.

- 3

- 6

to be the world’s

top IT powerhouse.We thrive to be the world’s top IT powerhouse.

Our mission is to lead innovations

in information technology, create lasting impact,

and educate next-generation leaders of the world.

- 4

- 6

to be the world’s

top IT powerhouse.We thrive to be the world’s top IT powerhouse.

Our mission is to lead innovations

in information technology, create lasting impact,

and educate next-generation leaders of the world.

- 5

- 6

are a key thrust

in EE researchAI and machine learning are a key thrust in EE research

AI/machine learning efforts are already a big part of ongoing

research in all 6 divisions - Computer, Communication, Signal,

Wave, Circuit and Device - of KAIST EE

- 6

- 6

Highlights

B.S. Candidate Do A Kwon (Prof. Jae-Woong Jeong) wins Outstanding Poster Award at the 2024 Spring Conference of The Korean Sensors Society & Sensor Expo Korea-Forum

B.S. student Do A Kwon (Advised by Jae-Woong Jeong) won the Outstanding Poster Award at the 2024 Spring Conference of The Korean Sensors Society & Sensor Expo Korea-Forum.

The Conference of the Korean Sensors Society is held biannually in spring and fall. This spring, it was held at the Daejeon Convention Center (DCC) from April 29 to 30th.

Do A Kwon, an undergraduate student, published a paper titled “Body-temperature softening electronic ink for additive manufacturing of transformative bioelectronics via direct writing” and was selected as the winner in recognition of her excellence.

The paper introduces body-temperature softening electronic ink that can be patterned in high resolution.

It is expected to open unprecedented possibilities in personalized medical devices, wearable electronics, printed circuit boards, soft robots, and more, pushing the existing limitations in electronic devices with fixed form factors.

0 Conference: 2024 Spring Conference of The Korean Sensors Society

0 Date: April 29-30, 2024

0 Award: Outstanding Poster Award

0 Authors: Do A Kwon, Simok Lee, Jae-Woong Jeong (Advisory Professor)

0 Paper Title: Body-temperature softening electronic ink for additive manufacturing of transformative bioelectronics via direct writing

<(from left) Professor Jae-Woong Jeong, Do A Kwon>

EE Professor Joung-Ho Kim Establishes NAVER-Intel-KAIST AI Joint Research Center(NIK AI Research Center) for the Development of Next-Generation AI Semiconductor Eco-System

EE Ph.D. candidate Subin Oh (Prof. Jae-Woong Jung) wins Best Paper Award at SPIE Smart Structures + NDE 2024

<(From left) Ph.D. candidate Subin Oh, Award Certificate>

Ph.D. student Subin Oh (Advised by Jae-Woong Jeong) won the Best Paper Award at SPIE Smart Structures + NDE 2024.

The SPIE Smart Structures + NDE brings together engineers and researchers as they share important advances that help move multifunctional materials, sensor systems, and structural health monitoring technologies into the future.

This conference was held from March 25 to 28 in Los Angeles, USA with over 450 papers presented. Ph.D. student Subin Oh presented the paper titled “Shape morphing magnetic materials using liquid metal for 3D electronics and soft robots”.

Professor Hoirin Kim’s research team wins ‘Best Student Paper Award’ at the International Conference on Acoustics, Speech, and Signal Processing (ICASSP)

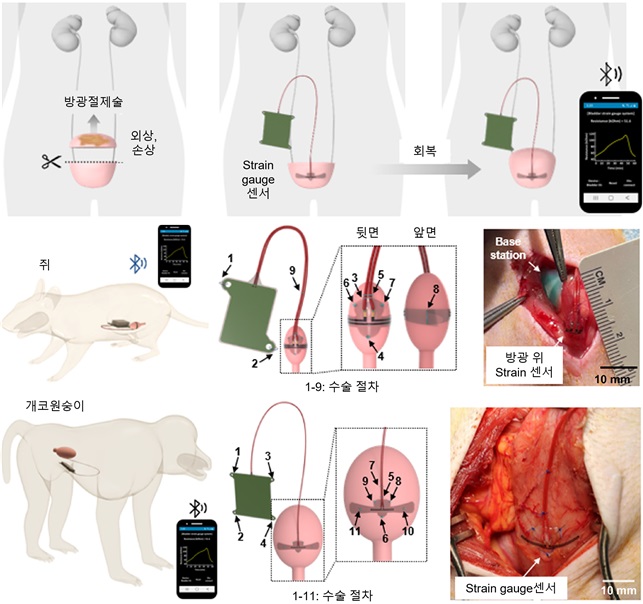

Professor Kyeongha Kwon’s Research Team Develops a Bioelectronic System for Monitoring Bladder Function After Surgery Using Electronic Sensors

*A catheter is a thin tube made of rubber or metal that is inserted into the bladder.

The research team led by Professor Kyeongha Kwon from the School of Electrical Engineering at KAIST announced on the 16th that they have developed digital healthcare technology that accurately measures the size and pressure changes of the bladder through joint research with Dr. Jihye Kim from Northwestern University in the United States.

Partial cystectomy* requires a long recovery period, during which the urinary tract’s ability to expel urine externally is intermittently assessed through urodynamic studies** (UDS). However, UDS is not patient-friendly, results can vary among users, and it is limited in its ability to collect continuous data. Furthermore, it can lead to the risk of catheter-associated urinary tract infections and, in high-risk patients, can progress to ascending pyelonephritis. As an appropriate alternative to UDS, there is a need for technology that can continuously and in real-time monitor the condition of the bladder without the insertion of a catheter.

*Partial cystectomy: A surgery that involves cutting out the tumor-bearing part of the bladder and stitching the rest of the bladder back together.

**Urodynamic studies: Diagnostic tests to assess the overall function of the bladder and urethra to plan treatment.

In response, the research team developed an implantable bladder platform that can wirelessly remotely measure mechanical deformation changes related to bladder filling and emptying. This system uses biodegradable strain sensors to measure the size and pressure changes of the bladder in real-time, and the sensors naturally dissolve and disappear within the body after the recovery period. This eliminates the need for additional surgery to remove the monitoring equipment, reduces the risk of complications, and improves patient comfort and recovery time.

Professor Kyeongha Kwon said, “Through extensive experiments using non-human primates (marmosets), we have demonstrated the efficacy of a device that provides accurate and reliable data on bladder function,” and added, “This can be used to shorten patients’ recovery time and improve overall surgical outcomes.”

The results of this study were published in the ‘Proceedings of the National Academy of Sciences (PNAS)’ on April 2nd. (Article title: A wireless, implantable bioelectronic system for monitoring urinary bladder function following surgical recovery, link: https://www.pnas.org/doi/abs/10.1073/pnas.2400868121?af=R)

This research was conducted with the support of the Basic Research Program, the Regional Innovation Lead Research Center Project, and BK21 funded by the Ministry of Science and ICT and the National Research Foundation of Korea.

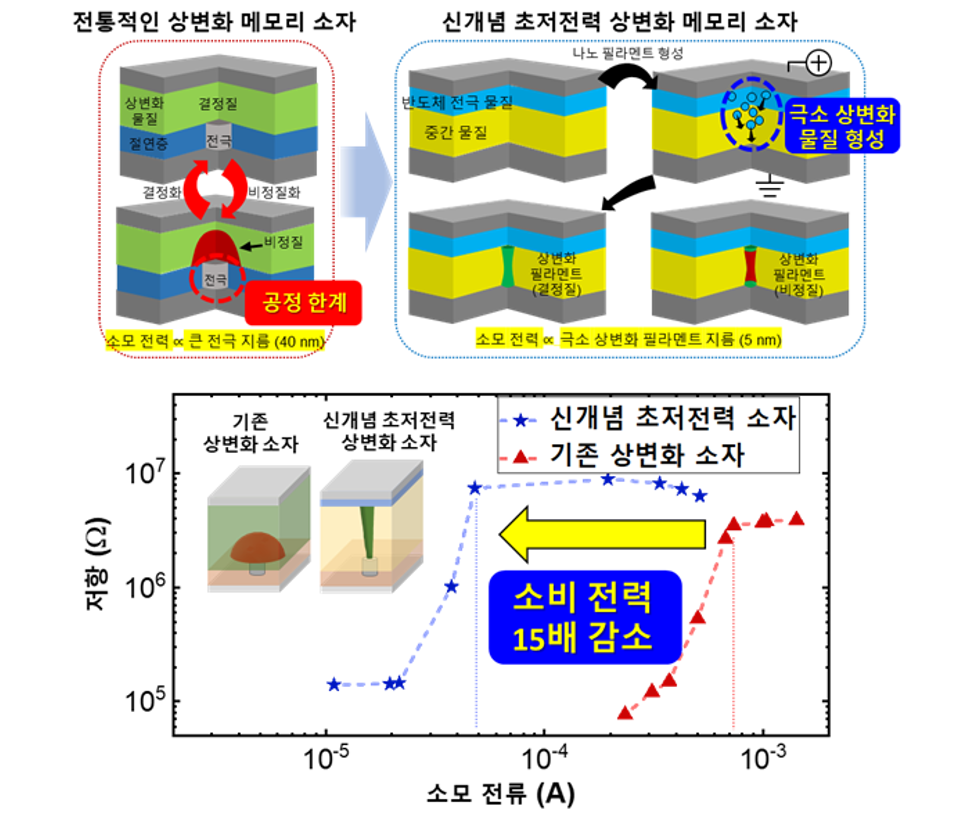

Professor Shinhyun Choi’s Research Team Develops Novel Semiconductor Device for Next-Generation Neuromorphic Computing/Memory (Published in Nature)

On the 4th, Professor Shinhyun Choi’s research team announced that they have developed an ultra-low power next-generation phase-change memory device that can replace DRAM (Dynamic Random-Access Memory) and NAND flash memory.

☞ Phase Change Memory: A memory device that stores or processes information by changing the resistance state through the use of heat to alter the material between amorphous and crystalline states.

Existing phase change memory devices are manufactured through expensive ultra-fine semiconductor lithography processes, requiring high power consumption. Previous research has focused on reducing the physical size of the device using ultra-fine semiconductor lithography processes to increase the heating effect for memory operation and lower power consumption.

However, this approach achieved only minor improvements in power efficiency and faced practical limitations due to increased process costs and complexity. Professor Choi’s team developed an ultra-low power phase change memory device that electrically forms extremely small nanometer-scale phase change filaments without the need for expensive lithography processes.

This not only significantly reduces process costs but also enables ultra-low power operation, offering a revolutionary advantage.

To address the power consumption issue of phase change memory, Professor Choi’s research team successfully developed an ultra-low power phase change memory device that consumes over 15 times less power than existing devices made through expensive ultra-fine lithography processes. This was achieved by electrically forming the phase change material in an extremely small manner.

EE Ph.D. candidates Park See-On and Hong Seokman participated as the first authors in this study. The research was published in the April issue of the renowned international academic journal `Nature’ on April 4th. (Paper title: Phase-Change Memory via a Phase-Changeable Self-Confined Nano-Filament)

< Figure 1: Diagram of the ultra-low power phase change memory device developed in this study, and a comparison of the power consumption reduction of the ultra-low power phase change memory device to existing phase change memory devices>

This research was supported by the Korea Research Foundation’s Next-Generation Intelligent Semiconductor Technology Development Project, the PIM Artificial Intelligence Semiconductor Core Technology Development (Device) Project, the Excellent Young Researcher Program, and the Nano Medical Device Development Project of the Nano Institute of Technology.

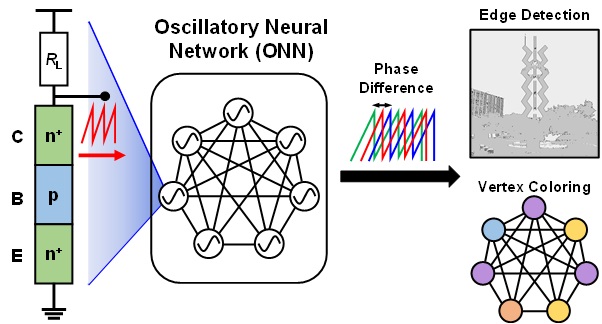

Professor Yang-Kyu Choi’s Research Team Solved Computing Challenges with Neuromorphic Neural Networks

*Graph coloring problem: A term used in graph theory, requiring different colors to be assigned to each vertex of a graph. This is similar to assigning frequencies to broadcasting stations to prevent overlap and the creation of areas with poor reception, and is widely applied in various fields.

The research team announced on the 3rd that they have developed a neuromorphic oscillatory neural network that mimics the interactions of biological neurons using silicon varistor components.

With the arrival of the big data era, artificial intelligence technology has made significant progress. One of the neuromorphic computing methods, the oscillatory neural network (oscillatory neural network), is an artificial neural network that mimics the interaction of neurons. The oscillatory neural network uses the connection operations of oscillators, which are the basic units, and performs calculations using oscillations rather than the magnitude of signals, thus offering advantages in terms of power consumption.

The research, led by Seong-Yun Yun, a doctoral student, and Professor Joon-Kyu Han from Sogang University, stated, “The developed oscillatory neural network can be used as neuromorphic computing hardware capable of calculating complex computing challenges, and is expected to be useful in resource allocation, new drug development, semiconductor circuit design, and scheduling,” highlighting the significance of the research.

The study, co-authored by Seong-Yun Yun and Professor Joon-Kyu Han, was published in ‘Nano Letters’, in its 24th volume, issue 9, on March 2024, and was selected as a supplementary cover article.

This research was conducted with the support of the Korea Research Foundation’s Next-Generation Intelligent Semiconductor Technology Development Project and the National Semiconductor Research Laboratory Support Core Technology Development Project.

Professor Kyeongha Kwon Appointed as Korea Representative of the IEEE ISSCC TPC