A research article authored by Jun-Hwe Cha (KAIST EE), Sang Yoon Yang (KAIST EE), Jungyeop Oh (KAIST EE), Shinhyun Choi (KAIST EE), Sangsu Park (SK Hynix), Byung Chul Jang (Samsung Electronics), Wonbae Ahn (KAIST EE) and Sung-Yool Choi (KAIST EE; Corresponding author) was published in Nanoscale (2020.07)

Article title: Conductive-bridging random-access memories for emerging neuromorphic computing

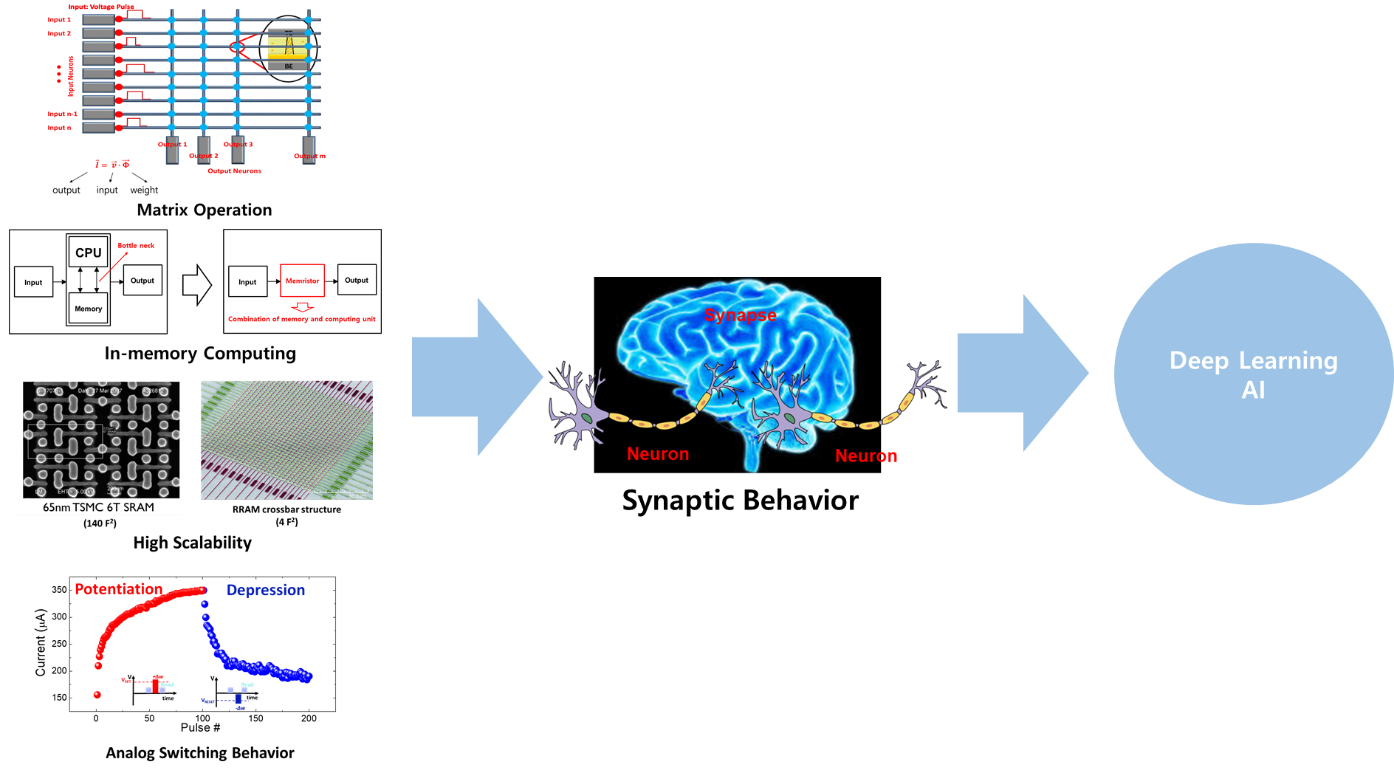

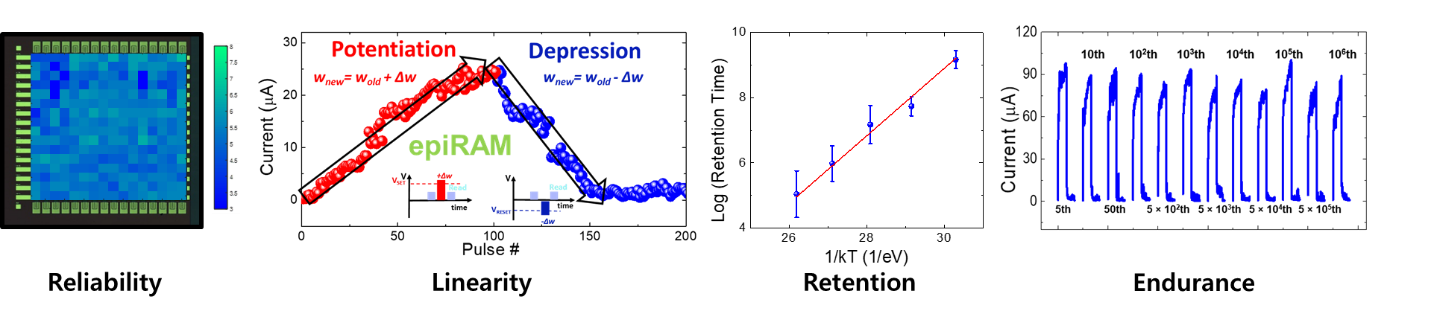

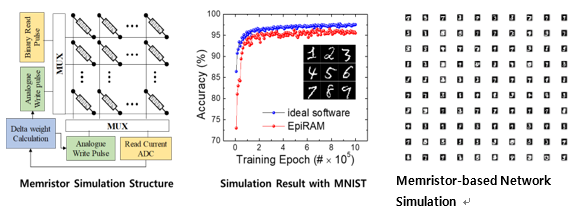

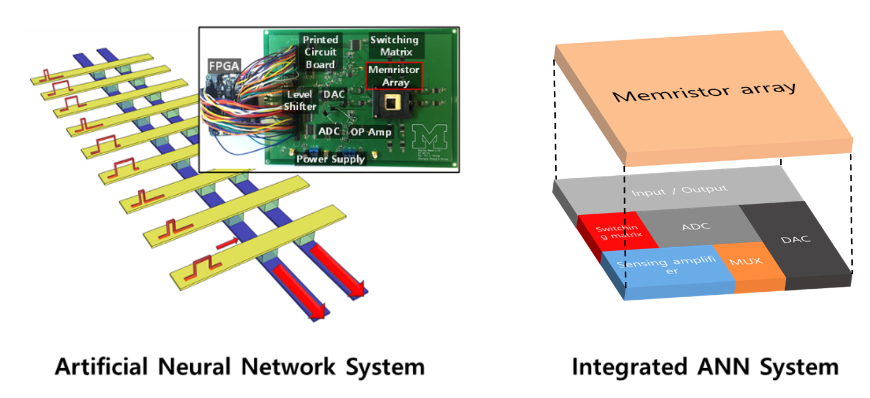

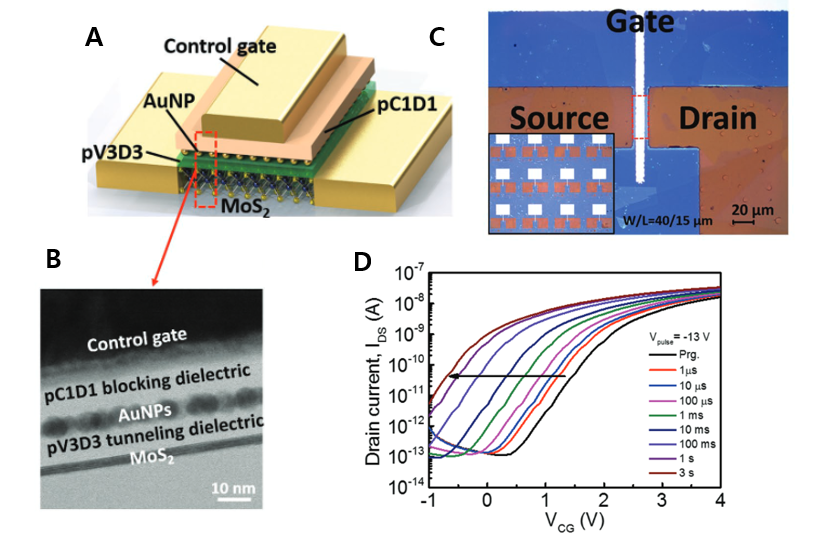

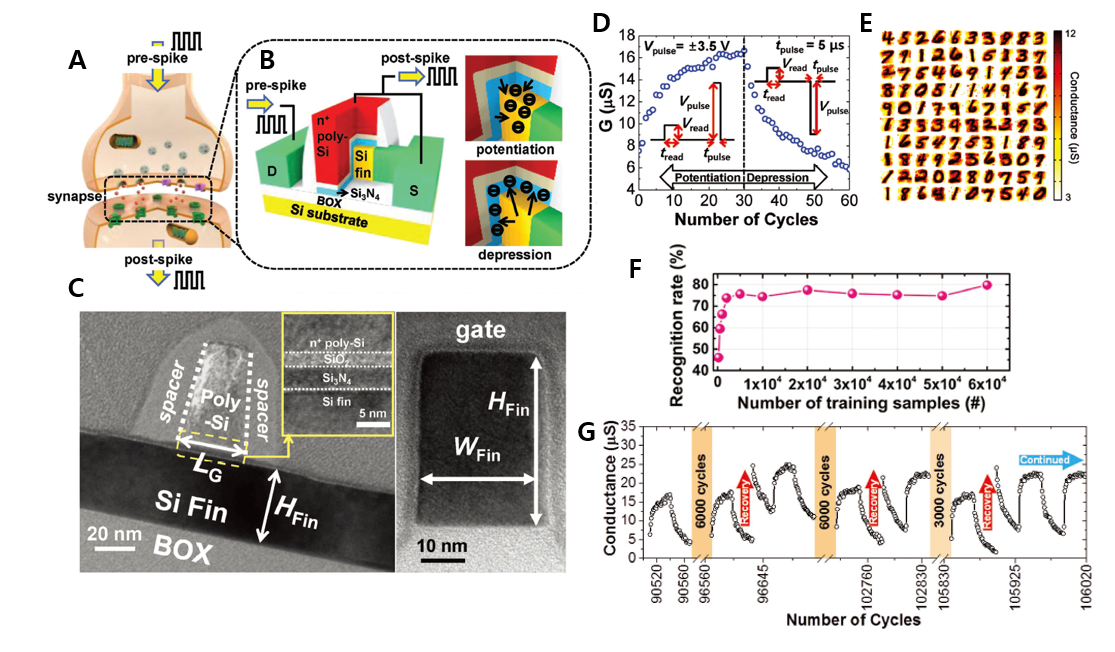

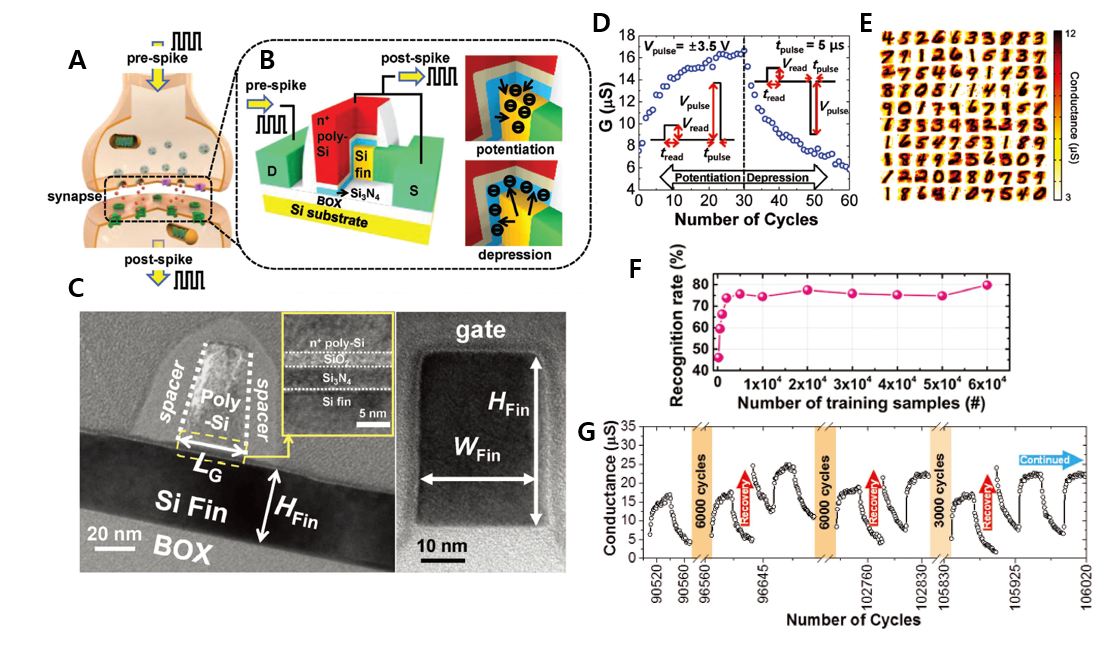

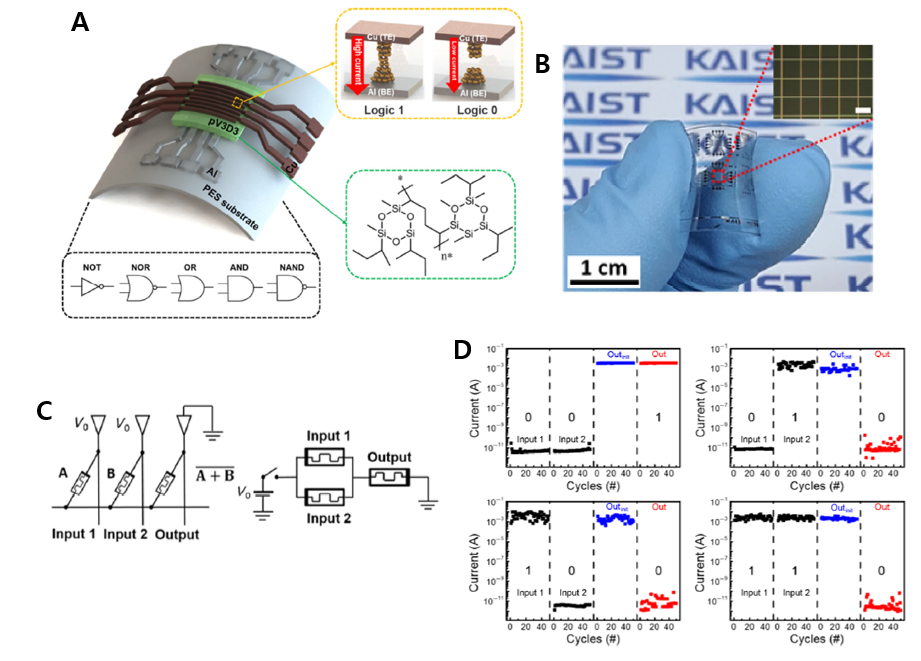

With the increasing utilisation of artificial intelligence, there is a renewed demand for the development of novel neuromorphic computing owing to the drawbacks of the existing computing paradigm based on the von Neumann architecture. Extensive studies have been performed on memristors as their electrical nature is similar to those of biological synapses and neurons. However, most hardware-based artificial neural networks (ANNs) have been developed with oxide-based memristors owing to their high compatibility with mature complementary metal–oxide–semiconductor (CMOS) processes. Considering the advantages of conductive-bridging random-access memories (CBRAMs), such as their high scalability, high on–off current with a wide dynamic range, and low off-current, over oxide-based memristors, extensive studies on CBRAMs are required. In this review, the basics of operation of CBRAMs are examined in detail, from the formation of metal nanoclusters to filament bridging. Additionally, state-of-the-art experimental demonstrations of CBRAM-based artificial synapses and neurons are presented. Finally, CBRAM-based ANNs are discussed, including deep neural networks and spiking neural networks, along with other emerging computing applications. This review is expected to pave the way toward further development of large-scale CBRAM array systems.

![AI in Device division 3 Shinhyun Choi's Research Laboratory [Memristor for AI]](https://ee.kaist.ac.kr/wp-content/uploads/drupal/최신현1_1.png)