Professor Jae-Hyeok Choi’s laboratory (Integrated Circuits and System Lab) in the Department of Electrical and Electronic Engineering of our university produced the winners of the Presidential Award at the 22nd Korea Semiconductor Design Competition.

[ (From left) PHD Student Yoon-seo Jo, Seon-eui Park, Joo-eun Bang]

‘The 22nd Korea Semiconductor Design Competition’ is a semiconductor design competition jointly hosted by the Ministry of Trade, Industry and Energy and the Korea Semiconductor Industry Association, aiming to discover creative ideas by cultivating the design ability of graduate students in the field of semiconductor design.

The recipients of the Presidential Prize are Seon-eui Park, Yoon-seo Jo, and Ph.D. student Joo-eun Bang of Professor Jaehyuk Choi’s lab. Their research on developing a chip based on the complementary metal oxide semiconductor (CMOS) process was selected for the Presidential Award.

[Professor Jae-Hyeok Choi]

6G communication is being studied with the goal of 1 terabps (Tbps). This is up to 50 times faster than 5G communication, which has a transmission speed of up to 20 Gigabps (Gbps). As the communication frequency band increases, a wider communication bandwidth can be used and data transmission speed can be increased. Therefore, it is essential to use a frequency band of 100 gigahertz (GHz) or more for the high data transmission speed required for 6G communication.

However, making an accurate reference signal using CMOS that can be used as a carrier wave in high frequency band is a challenge. Although CMOS process is advantageous for ultra-small and low-power design, its operating frequency and high-frequency band gain are limited, and low noise characteristics are disadvantageous compared to other existing processes such as SiGe and InP due to the difficulty in achieving ultra-low noise performance.

The chip developed by the students of Professor Jae-hyeok Choi’s team overcomes this limitation. They introduce an ultra-low-noise signal generation technology that can support high-order modulation and demodulation in the band above 100 gigahertz (GHz). This technology is expected to contribute to enhancing the price competitiveness and integration level of 6G communication chips to be commercialized in the future by demonstrating that the ultra-low noise performance required for 6G communication can be achieved even on the basis of the CMOS process.

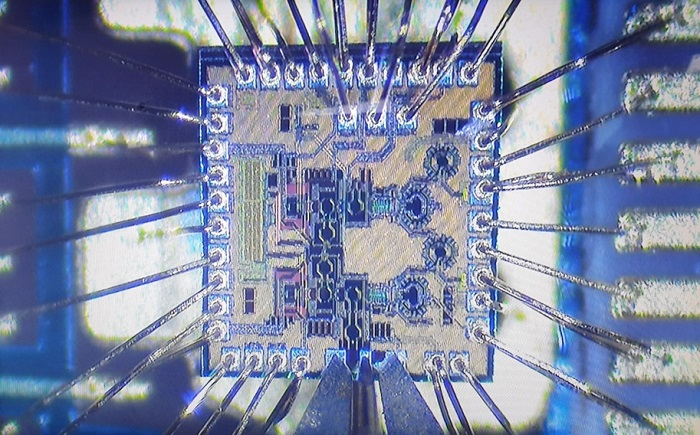

[Research result : Memory Chip picture]