Prof. Sung-Yool Choi & Sang-Hee Ko Park’s research group were reported in Yonhapnews, and 14 media, about implementing low-power memristor integrated circuit on February 13th, 2018.

This research is to provide a low-power nonvolatile flexible logic-in-memory circuit that suppresses sneak current and leakage current by integrating (1S-1M) memristors and selector devices.

The study was published as a cover paper in January 2018 in the international journal ‘Advanced Functional Materials’. (Impact factor 2018 : 13.325)

Media: ‘KAIST, memristor integrated circuit development to reduce power consumption‘

https://www.yna.co.kr/view/AKR20180213103900063?input=1195m

KAIST News: ‘Low-power, Flexible Memristor Circuit for Mobile and Wearable Devices’

https://www.kaist.ac.kr/_prog/_board/?mode=V&no=77021&code=ed_news&site_dvs_cd=en&menu_dvs_cd=0601&list_typ=B&skey=&sval=&smonth=&site_dvs=&GotoPage=9

KAIST EE: ‘Professor Choi Sung-Yool’s team published a cover paper on Advanced Funtional Materials’

https://ee.kaist.ac.kr/en/research-achieve/15609/

Article title: Memristive Logic‐in‐Memory Integrated Circuits for Energy‐Efficient Flexible Electronics

A research article authored by Byung Chul Jang (KAIST EE), Yunyong Nam (KAIST MSE), Beom Jun Koo (KAIST EE), Junhwan Choi (KAIST CBE), Sung Gap Im (KAIST CBE), Sang‐Hee Ko Park (KAIST MSE; Corresponding author), and Sung‐Yool Choi (KAIST EE; Corresponding author) was published at Advanced Functional Materials (2018.01)

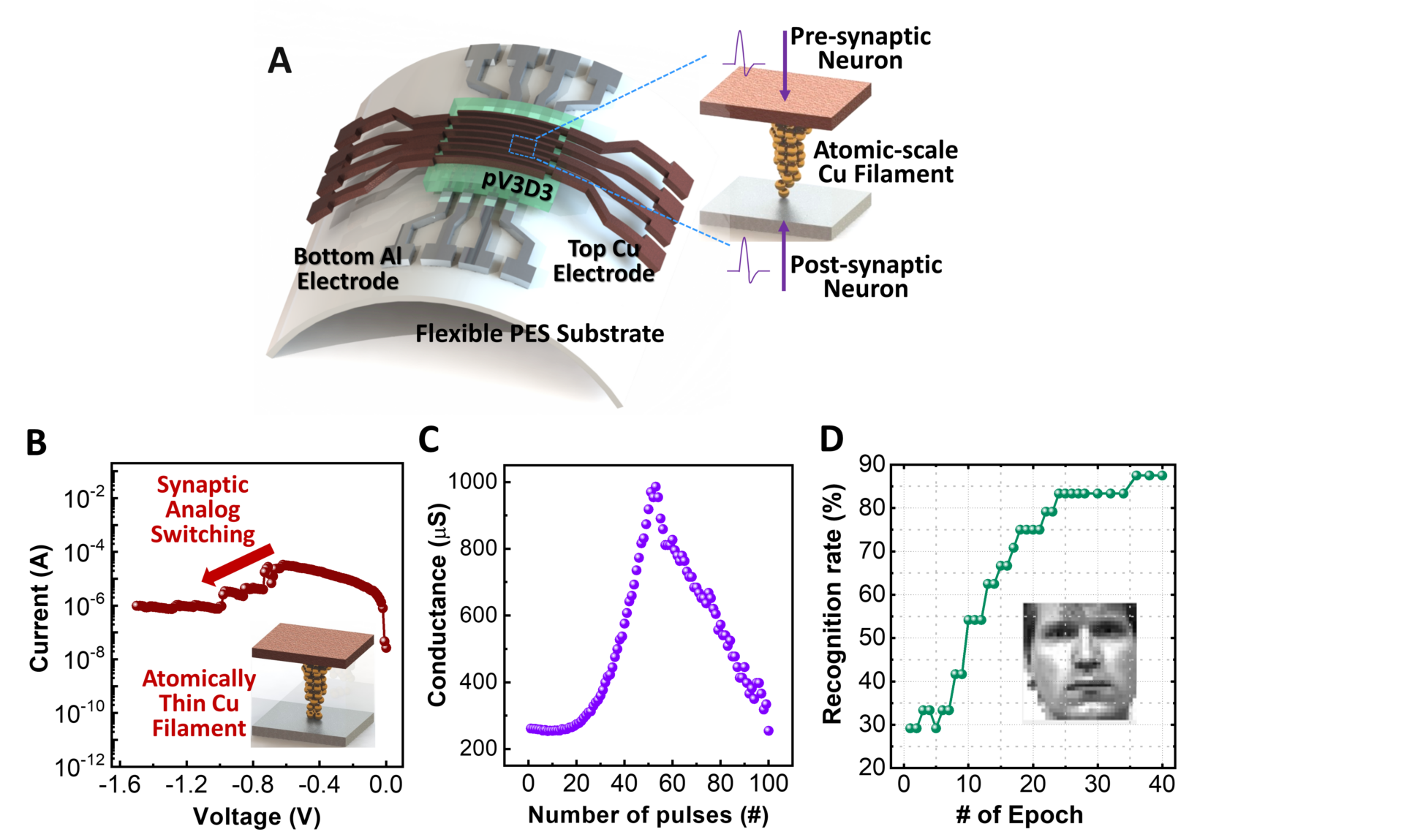

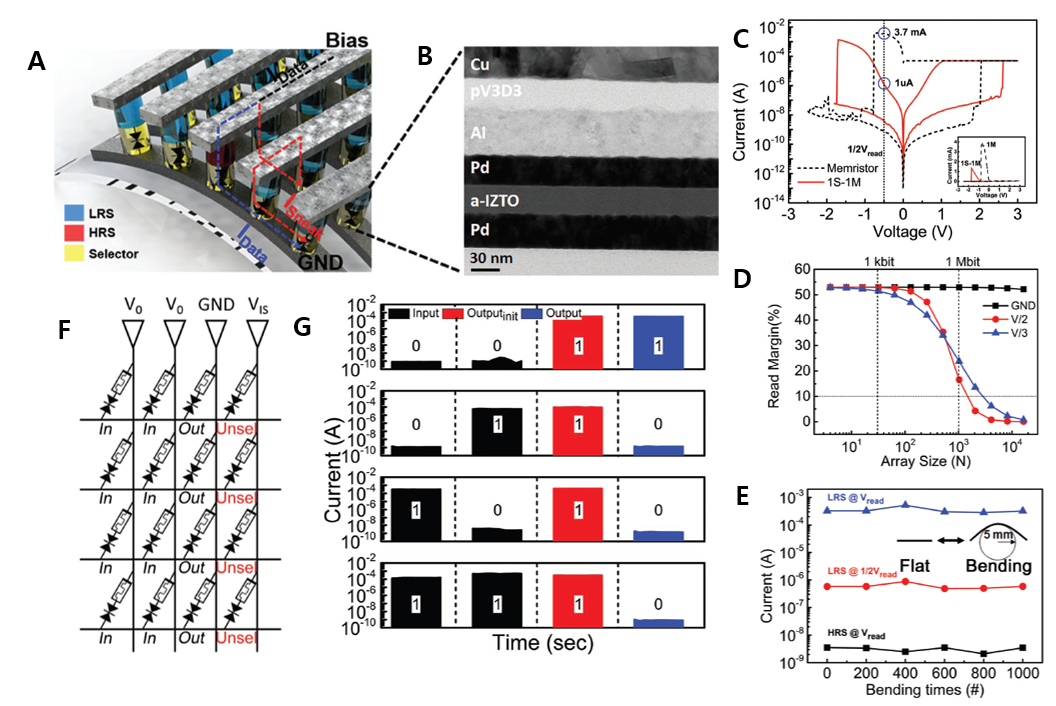

The use of von Neumann architecture, with its physically separate memory and processor, generates an extremely large energy-hungry data transfer between the memory and processor, inducing long latency and high power consumption. The memristor has been proposed as the fourth fundamental circuit element and can provide a creative solution to these problems. The memristor device has been widely investigated for a promising nonvolatile memory due to its simple structure, fast switching speed, low power consumption, and high packing density. The crossbar array is the optimal architecture enabling high packing density, defect tolerance, and logic operation; however, this architecture generates an inherent cell-to-cell interference problem. As this interference allows undesirable leakage currents known as “sneak currents” to flow through unselected devices during memristor operations, it limits the maximum array size and prevents the memristive nonvolatile logic-in-memory circuit from enabling parallel computing.

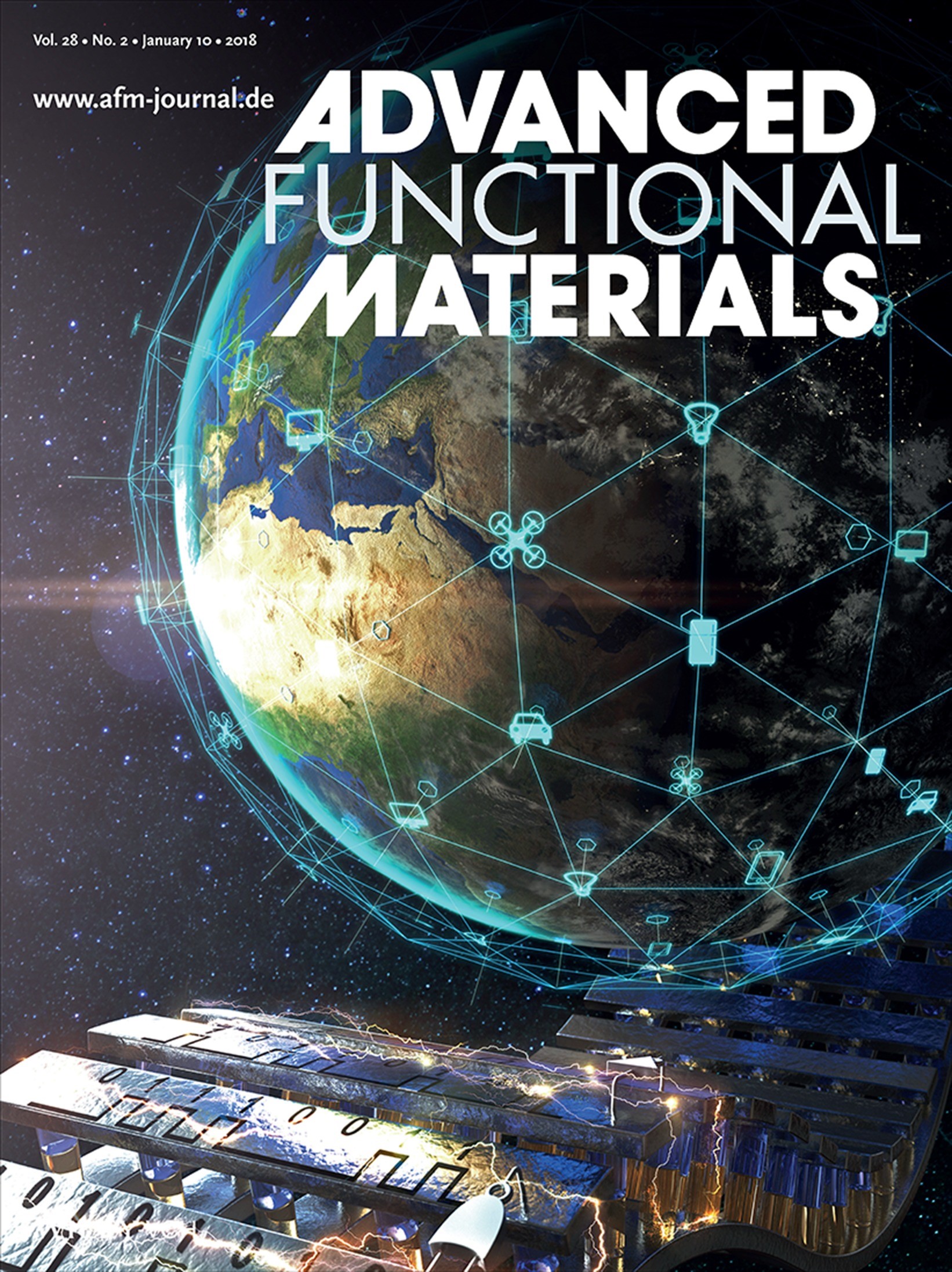

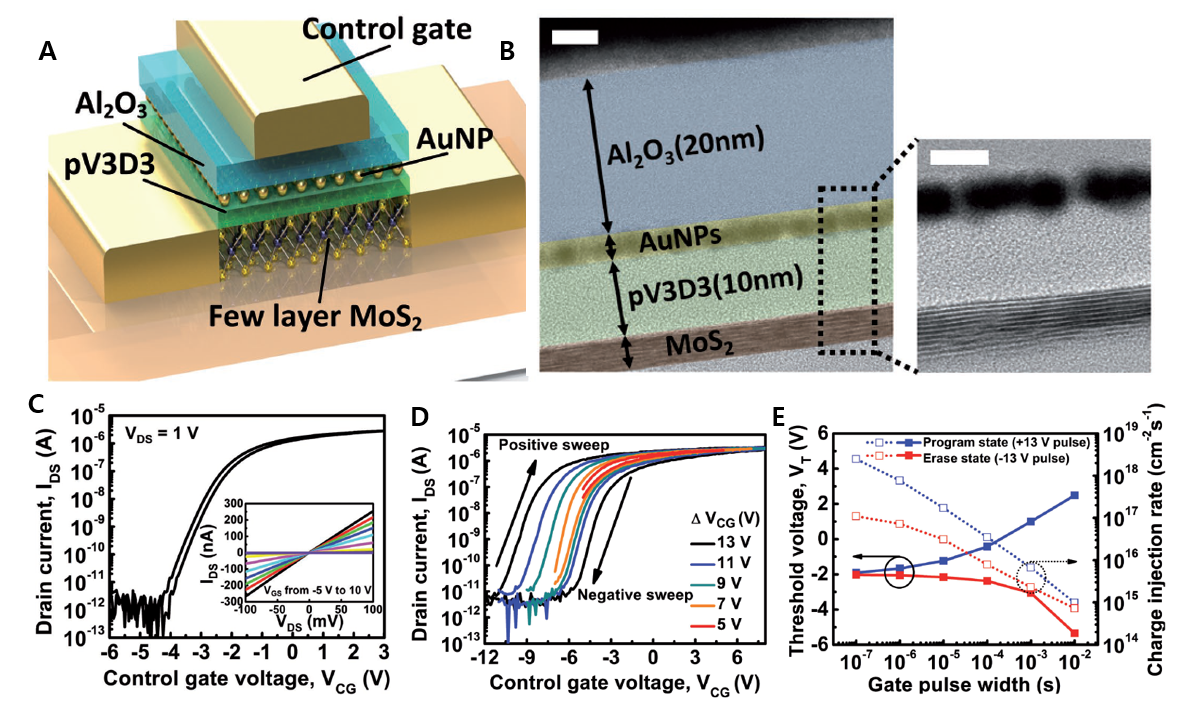

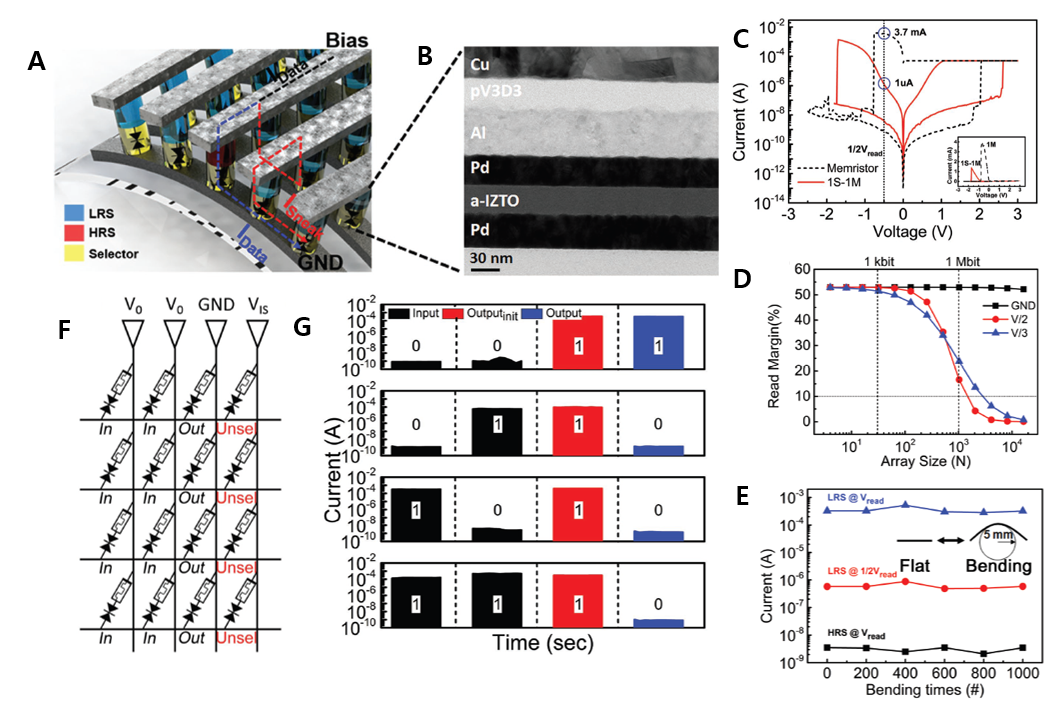

Herein, we develop a 1S–1M integrated circuit using a poly (1,3,5-trivinyl-1,3,5-trimethyl cyclotrisiloxane) (pV3D3)-based memristor and an a-IZTO-based selector on a flexible polyethersulfone (PES) substrate to propose a conceptual strategy for realizing an energy-efficient memristive nonvolatile logic-in-memory circuit, enabling parallel computing. The fabricated flexible a-IZTO-selector device exhibits outstanding stability against harsh electrical stress and mechanical strain. Using X-ray photoelectron spectroscopy (XPS) analysis and examining the I–V characteristics, effective removal of the a-IZTO SEAL via oxygen plasma treatment is confirmed. Thanks to this reliable and flexible a-IZTO selector, the 1S–1M integrated devices exhibit a significantly reduced leakage current under a low-voltage region compared to a 1M device, along with reliable switching performance against electrical and mechanical stresses. The reading margin of the 1S–1M array is evaluated under various operational schemes (ground, V/2, V/3), indicating a feasible maximum array size of more than 1 Mbit. We also experimentally demonstrate that the fabricated 1S–1M array can perform single-instruction multiple-data (SIMD), the basis of parallel computing, without interruption by the sneak current. We strongly believe that the proposed parallel computing method using a memristive nonvolatile logic-in-memory circuit can provide a low-power circuit platform for battery-powered flexible electronic systems with various potential applications.

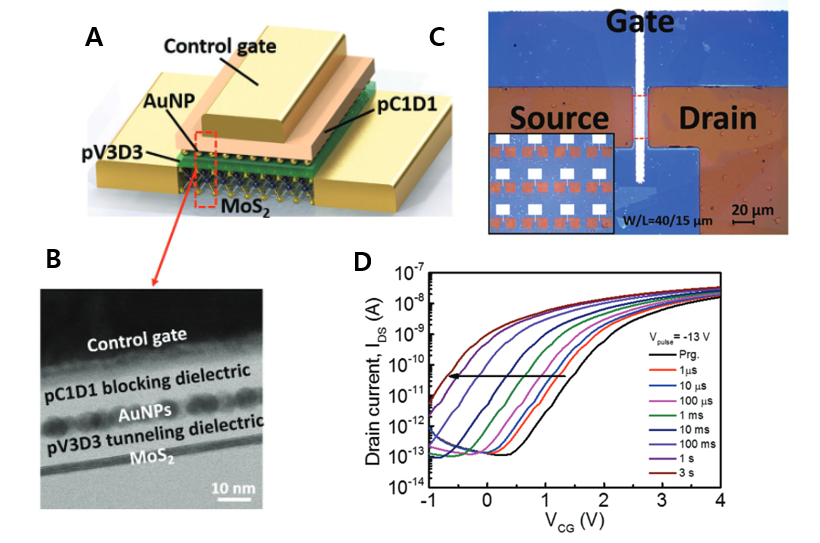

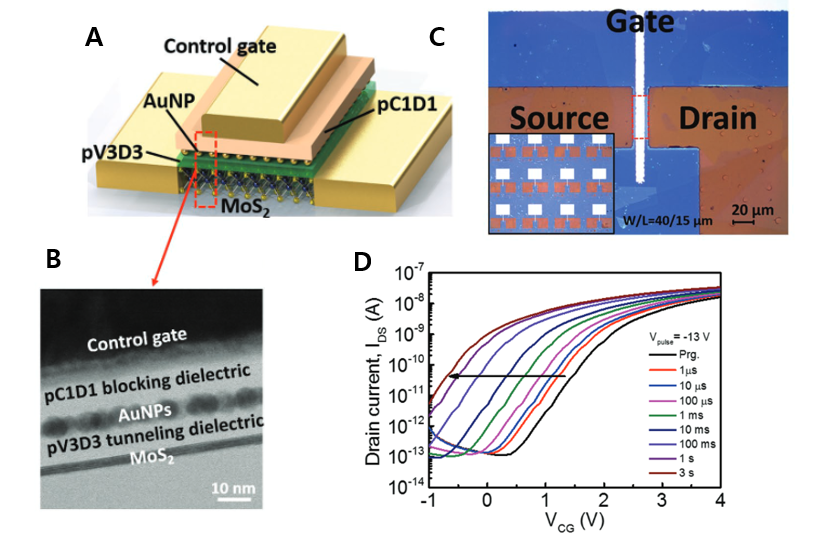

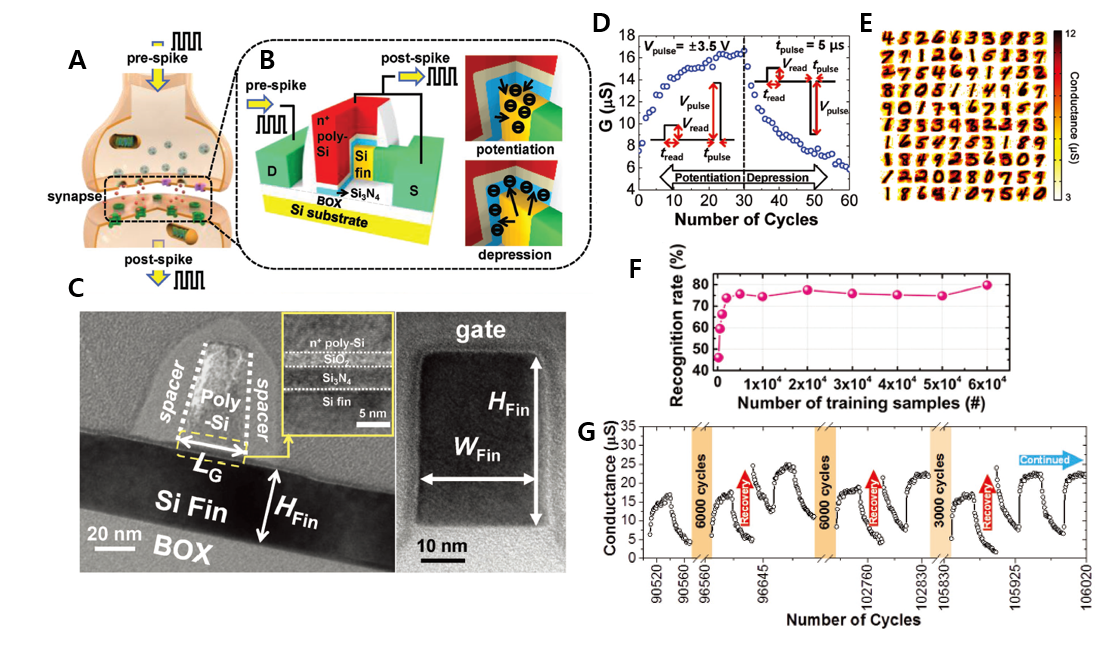

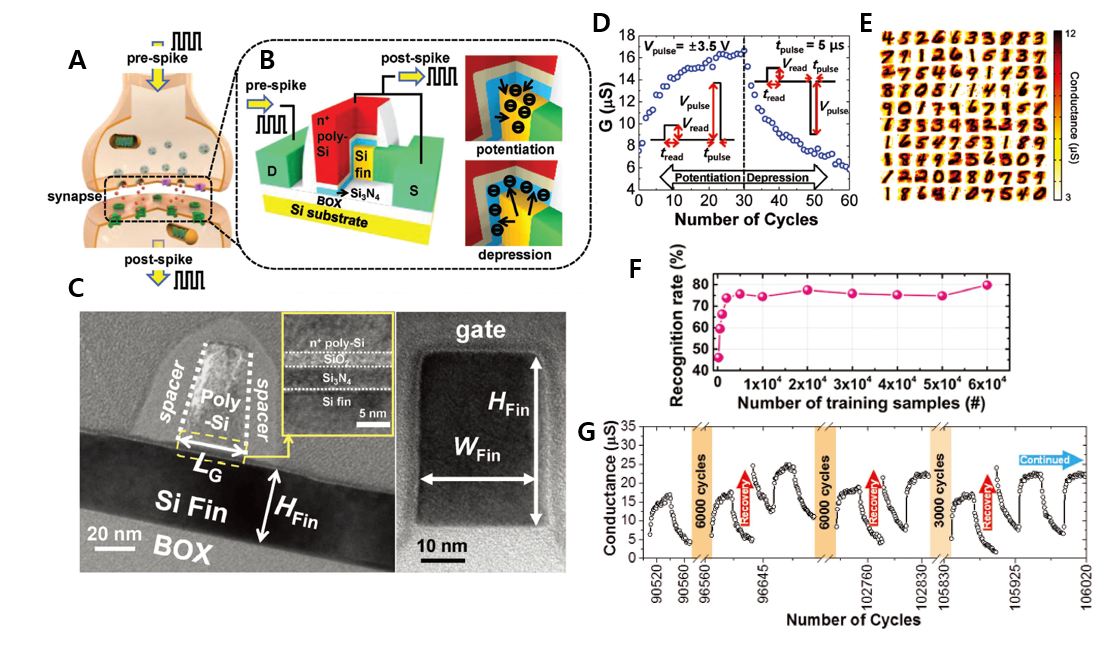

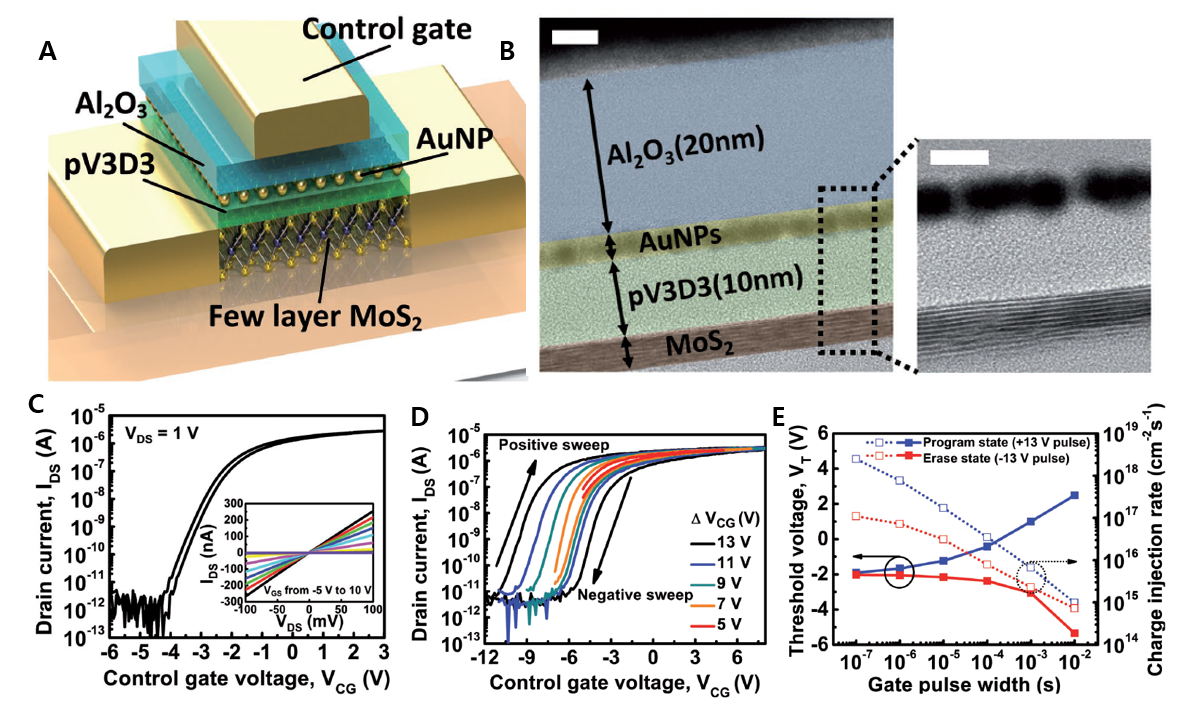

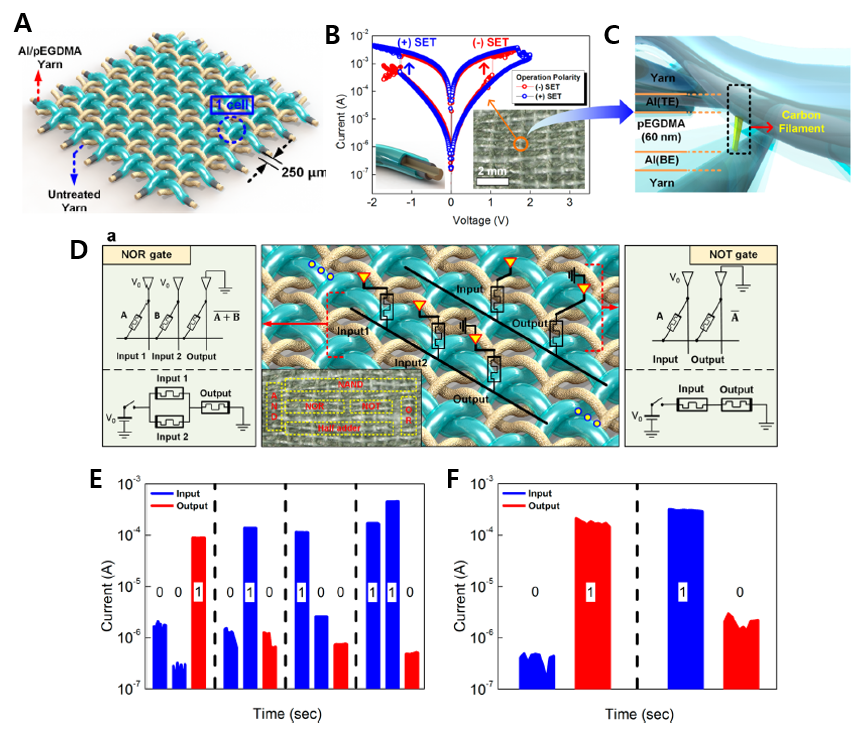

Figure 1. A Schematic illustration of integrated selector device role in memristor crossbar array during operation. B Cross-sectional TEM image of 1S–1M device. C Comparison of I–V characteristics of 1S–1M and 1M devices. Inset: Nonlinear I–V characteristics of 1S–1M device on linear scale compared with 1M device. D Calculated reading margin comparison for three reading bias schemes as function of array size. E Repetitive bending fatigue test for 1S–1M device. F Schematic of MAGIC-NOR gates within 1S–1M memristor array. G Experimental results for parallel operation of MAGIC-NOR gates.